# III-V on Silicon Lasers and Amplifiers Realized by Micro-Transfer Printing Integration Technology

Emadreza Soltanian

Doctoral dissertation submitted to obtain the academic degree of Doctor of Photonics Engineering

#### Supervisors

Prof. Günther Roelkens, PhD - Jing Zhang, PhD

Department of Information Technology

Faculty of Engineering and Architecture, Ghent University

December 2025

ISBN 978-94-93464-73-5 NUR 959, 965 Wettelijk depot: D/2025/10.500/133

### Members of the Examination Board

#### Chair

Prof. Em. Daniël De Zutter, PhD, Ghent University

#### Other members entitled to vote

Prof. David Marpaung, PhD, Universiteit Twente, the Netherlands Prof. Geert Morthier, PhD, Ghent University Prof. Pascual Muñoz, PhD, Universitat Politècnica de València, Spain Prof. Geert Van Steenberge, PhD, Ghent University

### **Supervisors**

Prof. Günther Roelkens, PhD, Ghent University Jing Zhang, PhD, Ghent University

### Dankwoord

This thesis and all the work presented here were not possible without standing on the shoulders of many, including all the scientists and researchers who developed this field step by step, and of course all the support I received from my family, friends, teachers, and professors throughout my educational journey.

So my first expression of thankfulness goes to my supervisors, Prof. Gunther Roelkens and Dr. Jing Zhang. Gunther trusted me with this doctoral position and gave me a lot of support, space to grow, and room to learn through many rounds of trial and error. He is not only a great scientist and boss, but also a personal role model to me, showing that it is possible to excel technically while still being a kind and wonderful human being. He proved that it is possible to gather many bright and passionate scientists and support them to bloom, to extend scientific and technical boundaries, and to push the field forward.

Jing supported me step by step throughout my PhD and beyond, up to this very day. I cannot count how many times he helped me, especially during my first MPW run, when I received thousands of errors with only a few hours left to submit. And when was that? At the beginning of COVID. I also learned many practical fabrication steps from him, truly one of the best. All of this, combined with his humility, is a lesson I will carry with me. I will do my best to contribute to society and to the scientific community in the same spirit as these two amazing individuals.

I would also like to thank Prof. Bart Kuyken, who supported me for about six months as my backup supervisor, and who, together with Dr. Camiel Op de Beeck, helped significantly with the laser linewidth measurements. And a big thanks to Prof. Kasper Van Gasse for valuable insights and constructive discussions on high saturation power SOAs.

Next, I would like to thank the amazing PRG for always being a positive supporter. Of course, this positive attitude comes from Prof. Em. Roel Baets, who has integrated it into the identity of PRG. I remember one of my first presentations, when I received many technical questions, but at the end, Roel simply asked me what I thought about the field and its future. That was an eye-opening moment for me. It gave me confidence to develop my own way of thinking and to form a broader view of the field, even as a first year PhD student. After all, the PhD title essentially says that the holder is a philosopher in the field.

I could continue for days mentioning PRG stories, but I need to keep this acknowledgement short to avoid exceeding my technical thesis pages. So I briefly express my deep thankfulness to Prof. Wim Bogaerts, Prof. Dries Van Thourhout, Prof. Geert Morthier, and all other PRG professors for their scientific support and discussions. I also thank my Master supervisors, Dr. Kambiz Abedi and Dr. Kian Jafari, who prepared me well for this journey.

Every PhD and postdoc in PRG knows that behind our progress, there is a very kind and supportive team. Thank you to Ilse Van Royen, Ilse Meersman, Kristien De Meulder, Bert Coryn, and Peter Guns for administrative and logistical support. In the CR, I received tremendous help from Liesbet Van Landschoot, Muhammad Muneeb, Steven Verstuyft, Elif Ozceri Iyikanat, and Peter Geerinck.

When fabrication goes well and I get a tiny but shiny sample, I always go to the fourth floor to see if it actually shines. The champions of the Measurement Lab are always there to help, including Clemens Krickel, Hasan Salmanian, and in my first year, Jasper Jans. I also thank the MPW and IPKISS experts, Umar Khan, Ewoud Vissers, and Laurens Bogaerts. Sometimes I ask them silly questions like why my script does not run, and they immediately know that I need to run my IDE as administrator. You thought my OpenVPN was off? No, it was on.

Throughout the years, what kept us alive during the hard work was the positive atmosphere and the funny conversations in the office. Special thanks to the 150.032 group, from all the former officemates now continuing their journey elsewhere, including Alexandros Liles, Ali Raza, Meryem Benelajla, Biwei Pan, and the funniest of all, Irfan Ansari, and also former officemates on other floors like Clemens. And to the long term 150.032 members, Jing Zhang, Mattias Verstuft, and Chupao Lin. And of course to the current 150.032 members, Michele Zenari, Evangelia Delli, Tiernan McCauphery, Yu Xue, Yang Liu, Mouhamad Al Mahmoud, and Ye Chen. Thank you for all the small talks and positive energy in the office and during lunches. By the way, where is Manuel Manta Chapa?

Speaking of former PRG members, I also want to thank Javad Rahimi Vaskasi, Bahawal Haq, Camiel Op de Beeck, Mahmoud Shahin, Alejandro Diaz Tormo, Jeroen Goyvaerts, Artur Hermans, Stijn Cuyvers, Grigorij Muliuk, Hong Deng, Soren Dhoore, Gilles Feutmba, Xin Guo, Kamalpreet Kaur, Zhongtao Ouyang, Cenk Ibrahim Ozdemir, Abdul Rahim, Khannan Rajendran, Dennis Maes, Sulakshna Kumari, Anton Vaseliv, Haolan Zhao. All of you remind me that I joined PRG a long time ago and still had not defended. Time really flies.

I am truly grateful to all the current PRG members as well. I promise to only mention a few top of my head, Jasper De Witte, Yujie Guo, K. P. Nagarnajun, Ivo Tanghe, Dongbo Wang, Antonietta Parracino, Thomas Vervust, Max Kiewiet, He Li, Enes Lievens, Isaac Luntadila Lunfungula, Korneel Molkens, Stijn Poelman, Senbiao Qin, Luis Reis, Lukas Van Iseghem, Andualem Ali Yimam, and all the Toms (Vanackere, Vandekerckhove, Reep). And also IDLab friends, Nishant Singh, Joris Van Kerrebrouck, and Jakob Declercq. You can see clearly that I was not biased toward the uTP group. To add your name here, please see the pricing list at the end. Sorry, my intrusive thoughts won. Enough with the jokes.

As I mentioned earlier, Gunther and Bart gathered many bright and hardwor-

king colleagues in TRANSVERSE, and I am proud to be a member of it. Thank you to all the TRANSVERSE colleagues for the coherent efforts, including Jing Zhang, Sarah Uvin, Maximilien Billet, Laurens Bogaerts, Ali Uzun, Michele Zenari, Evangelia Delli, Elif Ozceri Iyikanat, Emiel Dieussaert, Tiernan McCauphery, Suzanne Bisschop, Philip Ekkels, Lam Tran, Margot Niels, and Ye Chen. I believe we can make an impact in the field, and we are going to.

I would also like to thank the WON team, especially Prof. Wladek Forysiak, Antonio Napoli, and Tatiana Kilina, for empowering all 14 PhD ESRs in this H2020 Marie Sklodowska Curie project. Thanks as well to Behnam Shariati, Rasoul Sadeghi Yamchi, Bruno Correia, Elliot London, Rafael Kraemer, Pratim Hazarika, Thyago Monteiro, Alex Donodin, and Gabriele Di Rosa for the great times during the WON training events.

If it was not for EU taxpayers and the brilliant minds who create and organize Horizon like and Marie Curie like programs to support scientists and develop science and technology, this thesis might have taken another decade. So thank you, even if I do not know you.

Thank you to wonderful Flanders, especially beautiful Gent, and its supportive people during difficult times, especially during COVID, who treated me, as a foreigner, as one of their own. And thank you for preserving such a fantastic city. Every time I walk from Sint Baafsplein to the Stadshal, to Klein Turkije, to Korenmarkt, and to the Graslei-Korenlei, my mind and energy get refreshed. I always feel that J. K. Rowling must have walked through here, and then everything started.

Now, to my friends who see our good and bad sides and still keep running with us through life, making its sweet and sour moments joyful. Thank you Javad Rahimi, Shahriar Nategh, Shima Arambash, Hossein SeyyedAghaei and his wonderful family, Javadoo, Pouya DeBoer, Behnam Madadnia, Arash Abyaz, Saeid Adeli, Amirreza Seraj, Pooya Poolad, Ali Hadizadeh, Saeed Misaghian, Mojtaba Abbasnejad (R.I.P.), Keyvan Keramatzadeh, Amin Samghani, Reza Jalali, Masoud Azarbeyg, Mohammad Kianfard, MohammadReza Narimani, Saber Neisi Minaei, and Mohammad Azizdoost.

If you are easy to cry, skip this part.

To my beloved family, who always supported me even during their own difficult times, even when they never had the same support they gave me. My dad, Iraj Soltanian, and my mom, Fatemeh Joulaei Jahani, from whom I learned the meaning of life. They are heroes to me, the embodiment of persistence, kindness, caring for others, and staying humble even in the toughest moments.

Thank you to my parents in law, Bakhtiar Kia and Nasrin Ahmad Khan Beigi, from whom I learned responsibility and giving others a chance for a better tomorrow.

Throughout my life I have mostly been a quiet and home staying person, but my wonderful siblings always shared their life experiences and showed me the real world through different phases. They mentored me in how to thrive and how to build positive connections with people. Thank you for taking care of me and making me a better person every day, Shafa, Captain Hossein, Mohsen, Sana, and my siblings in law, Farzin Farshad, from whom I learned kindness and respect, Zahra, Hanna, Milad, Faeze, and Mehrdad. And thank you to the sweetest parts of life, my niblings, Matin, Yasi, and Selena. I miss you and I miss the nonsense games I created to keep your minds busy.

Finally, heartfelt thanks to my Knight, Dr. Ghazaleh Kia, my lovely wife, my best friend, and my partner in crime. I am always amazed and inspired by your hard work, persistence, your desire to make a positive impact, and your unlimited kindness that you spread to everyone. Thank you for making my life a valuable gift. I am proud of you and proud to be with you.

Thank you all for everything.

Gent, December 2025 Emadreza Soltanian

### Table of Contents

| Da | ankwo  | oord                                                             | 1    |

|----|--------|------------------------------------------------------------------|------|

| Ne | ederla | andse samenvatting x                                             | xvii |

| Er | nglish | summary                                                          | xiii |

| 1  | Intr   | roduction                                                        | 1-1  |

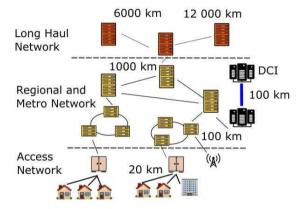

|    | 1.1    | Optical Fiber Network                                            | 1-1  |

|    |        | 1.1.1 Optical Fiber Communication Links                          | 1-3  |

|    |        | 1.1.2 Optical Interconnects                                      | 1-4  |

|    | 1.2    | Integrated Photonics                                             | 1-5  |

|    | 1.3    | Silicon Photonics                                                | 1-6  |

|    |        | 1.3.1 Introduction                                               | 1-6  |

|    |        | 1.3.2 IMEC Silicon Photonics Platforms                           | 1-8  |

|    | 1.4    | Integration Techniques for Silicon Photonics                     | 1-14 |

|    |        | 1.4.1 Hybrid Integration                                         | 1-15 |

|    |        | 1.4.2 Heterogeneous Integration                                  | 1-17 |

|    |        | 1.4.3 Micro-Transfer Printing Integration Method                 | 1-22 |

|    | 1.5    |                                                                  | 1-27 |

|    | 1.6    | Publications and Awards                                          | 1-28 |

|    |        | 1.6.1 Publications in international peer reviewed journal papers | 1-28 |

|    |        | 1.6.2 Publications in international conference proceedings       | 1-30 |

|    |        | 1.6.3 Awards                                                     | 1-32 |

|    | Refe   | erences                                                          | 1-33 |

| 2  | Ultr   | ra-wide Tunable Narrow-linewidth III-V on Si Laser               | 2-1  |

|    | 2.1    | $\epsilon$                                                       | 2-2  |

|    |        | 2.1.1 OIF 400G-ZR Standard                                       | 2-3  |

|    | 2.2    | Design                                                           | 2-4  |

|    |        | 2.2.1 Building Blocks of a III-V-on-Si laser                     | 2-5  |

|    |        | 2.2.1.1 Si-Waveguide                                             | 2-7  |

|    |        |                                                                  | 2-8  |

|    |        | 2.2.1.3 Multi-mode-interfrometer (MMI)                           | 2-9  |

|    |        | 2.2.1.4 Pre-fabricated micro-transfer-printing compati-          |      |

|    |        | ble SOA                                                          | 2-11 |

|   |      | 2.2.1.5 Highly Reflective Filter                                   |      |

|---|------|--------------------------------------------------------------------|------|

|   |      | 2.2.2 Design of Tunable Narrow-Linewidth Laser                     | 2-20 |

|   |      | 2.2.2.1 Ring Resonator Based Filters                               | 2-20 |

|   |      | 2.2.2.2 Theory of Laser Linewidth                                  | 2-23 |

|   |      | 2.2.2.3 Design of Laser's Filter and Passives                      | 2-27 |

|   |      | 2.2.3 Design of Ultra-Wide Tunable Narrow-Linewidth Laser .        |      |

|   | 2.3  | Fabrication                                                        |      |

|   |      | 2.3.1 SOI Fabrication                                              | 2-32 |

|   |      | 2.3.2 SOA Fabrication                                              |      |

|   |      | 2.3.3 Integration and Post-Processing                              | 2-39 |

|   | 2.4  | Characterization                                                   |      |

|   |      | 2.4.1 Laser Tunability                                             | 2-42 |

|   |      | 2.4.2 Linewidth characterization                                   |      |

|   |      | 2.4.2.1 Narrow-linewidth measurement methods                       | 2-44 |

|   |      | 2.4.2.2 Linewidth measurement results of the fabricated            |      |

|   |      | lasers                                                             | 2-46 |

|   |      | 2.4.3 Comparison with State-of-the-Art                             |      |

|   | 2.5  | Broader Application Demonstrators                                  |      |

|   |      | 2.5.1 Biomedical Sensing Applications                              |      |

|   |      | 2.5.1.1 Heartbeat Monitoring                                       |      |

|   |      | 2.5.1.2 Spectroscopy                                               |      |

|   |      | 2.5.2 Gas Sensing                                                  |      |

|   |      | 2.5.3 Linewidth-Reduced Laser for Coherence-Critical Appli-        |      |

|   |      | cations                                                            | 2-55 |

|   |      | 2.5.4 Programmable Photonics                                       | 2-57 |

|   | 2.6  | Conclusion                                                         |      |

|   | Refe | rences                                                             | 2-61 |

|   |      |                                                                    |      |

| 3 |      | ro-Transfer Printing Compatible High Saturation Power SOA          | 3-1  |

|   | 3.1  | Aiming for $\mu$ TP-compatible High Saturation Power SOA           |      |

|   | 3.2  | Design                                                             |      |

|   | 3.3  | Fabrication                                                        |      |

|   |      | 3.3.1 SOI Fabrication                                              |      |

|   |      | 3.3.2 SOA Fabrication                                              |      |

|   |      | 3.3.3 Integration and Post-Processing                              |      |

|   | 3.4  | Characterization                                                   |      |

|   | 3.5  | Conclusion and Future Works                                        |      |

|   | Refe | erences                                                            | 3-24 |

| 1 | Tow  | ards Wafer Scale $\mu$ TP Integration                              | 4-1  |

|   | 4.1  | Introduction                                                       | 4-2  |

|   | 4.2  | Essential Tools and Processes for Wafer-Scale $\mu$ TP Integration | 4-3  |

|   |      | 4.2.1 Spray Coater – EVG®101                                       | 4-3  |

|   |      | 4.2.2 µTP Printer – ASMPT Amicra NANO                              |      |

|   | 4.3  | Initial Demonstration of Wafer-Scale $\mu$ TP                      |      |

|   |      | r                                                                  |      |

|   | 11   | <ul> <li>4.3.1 BCB Spray Coating Optimization on Blank Si Wafers</li> <li>4.3.2 Demonstration of Wafer-Scale μTP of IIIV on Si</li> <li>Conclusion and Future Work</li> </ul> | 4-10             |

|---|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|

|   | 7.7  | Conclusion and Future work                                                                                                                                                    | <del>4</del> -13 |

|   | Refe | erences                                                                                                                                                                       | 4-15             |

| 5 | Con  | clusion and Outlook                                                                                                                                                           | 5-1              |

|   | 5.1  | Key Contributions                                                                                                                                                             | 5-2              |

|   | 5.2  | Towards an Ecosystem for Wafer-Scale $\mu$ TP Integration                                                                                                                     | 5-3              |

## List of Figures

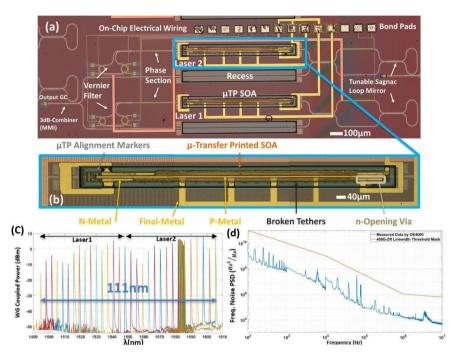

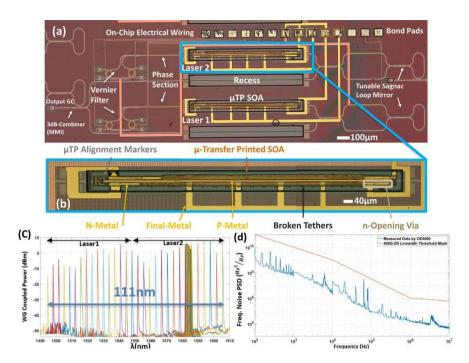

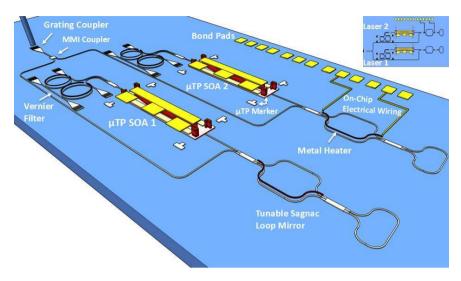

| 1 | Demonstratie van ultra-breed afstembare III-V-op-Si-lasers met smalle lijnbreedte, geïntegreerd op IMEC 400nm+ platform. (a) Schematische weergave van de laserarchitectuur met Vernier-filters gebaseerd op microringresonatoren en Sagnac-lusspiegels voor enkelmodige werking en lijnbreedtereductie. Een dubbele laserconfiguratie maakt afstemming mogelijk buiten de versterkingsbandbreedte van individuele SOA's. (b) Close-up van de transfer-geprinte SOA met finale metallisatie. (c) Gemeten afstembereik van meer dan 110 nm over het gecombineerde laserspectrum. (d) Lijnbreedtemetingen met de OEwaves OE4000 bevestigen Lorentz-profielen ruim onder de 400G-ZR-drempel van 500 kHz xxviii                                               |

|---|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

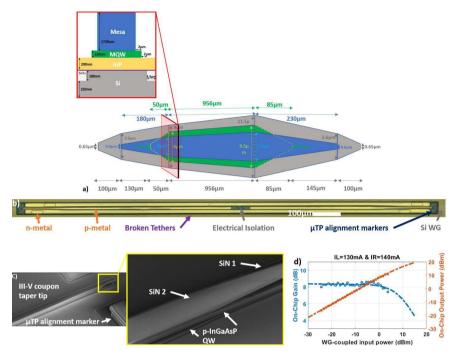

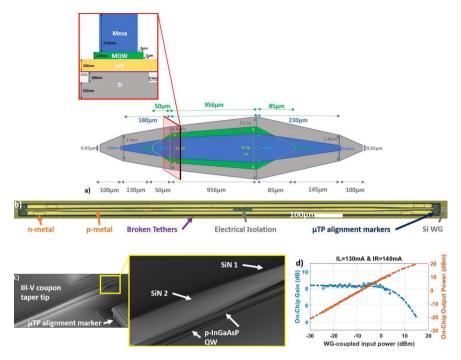

| 2 | Demonstratie van een nieuw hybride III-V-op-Si tapervormig ontwerp voor SOA's met hoge verzadigingsvermogens. (a) Schematische weergave van de getaperde SOA-structuur met een geleidelijk verbredende actieve regio en siliciumgolfgeleider om de optische opstelling te optimaliseren en het verzadigingsvermogen te verhogen. (b) Microscopisch beeld van de transfer-geprinte SOA op een E-beam rapid prototyping siliciumstaal. (c) SEM-dwarsdoorsnede van de taperpunt en $\mu$ TP-uitlijningsmarkeringen. (d) Gemeten onchip versterking van 8,36 dB en uitgangsvermogen versus toenemend ingangssignaal, waaruit een verzadigingsvermogen van 18,4 dBm wordt afgeleid, wat de effectiviteit van de getaperde SOA als booster-versterker bevestigt |

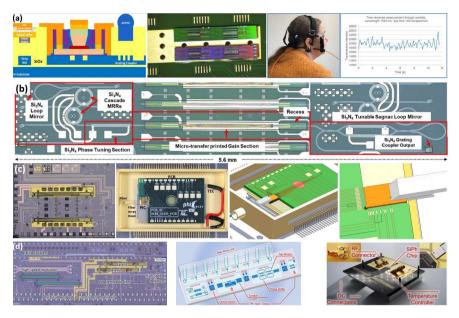

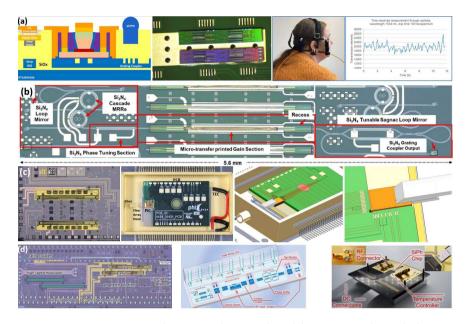

| 3 | Demonstratoren die de veelzijdigheid van het III-V-op-Si laser-platform buiten telecomtoepassingen aantonen. (a) µLens-gemonteerde laser-PIC gebruikt voor biomedische sensing via hartslagmonitoring door transmissie via de oorlel. (b) Hybride III-V-op-SiN laser met lijnbreedtes onder de 25 kHz voor toepassingen waarbij coherentie cruciaal is, zoals LiDAR. (c) Verpakte SiPh-laser met geïntegreerde golflengtemonitoring en vergrendeling voor gassensing. (d) Programmeerbare fotonische chip met dynamische herconfigureerbaarheid, die de brede inzethbaarheid van het geïntegreerde laser- en versterkerplatform illustreert                                                                                                               |

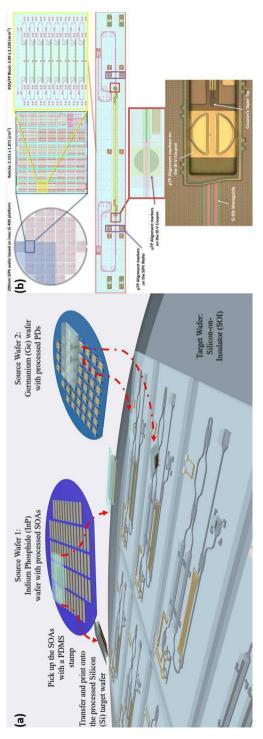

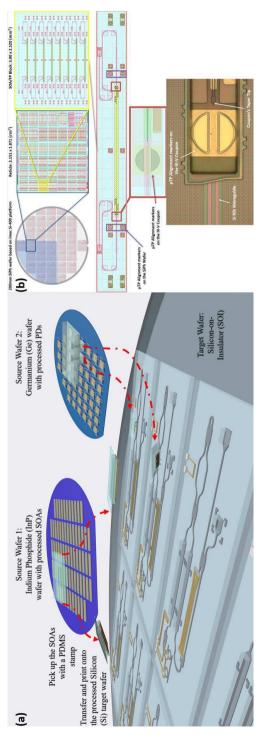

| 4   | Overgang van chipniveau naar waferniveau $\mu$ TP-integratie binnen de Transverse pilotlijn. (a) Overzicht van $\mu$ TP-integratie op waferschaal. (b) Demonstratie van $\mu$ TP-integratie op wafer-schaal van III-V-coupons op een 200 mm SiPh-wafer, met submicron uitlijningsprecisie en een printopbrengst van $100\%$                                                                                                                                                                                                                                                                                                                                  | xxxi  |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| 5   | Demonstration of ultra-wide tunable narrow-linewidth III-V-on-Si lasers integrated on IMEC 400nm+ platform. (a) Schematic of the laser architecture featuring Vernier filters based on microring resonators and Sagnac loop mirrors for single-mode operation and linewidth reduction. A dual-laser configuration enables tuning beyond the gain bandwidth of individual SOAs. (b) Close-up of transfer-printed SOA with final metallization. (c) Measured tuning range exceeding 110 nm across the combined laser spectrum. (d) Linewidth characterization using OEwaves OE4000 confirms Lorentzian linewidths well below the 400G-ZR threshold of 500 kHz. | xxxiv |

| 6   | Demonstration of a novel hybrid III-V-on-Si tapered design for high saturation power SOAs. (a) Schematic of the tapered SOA structure with a gradually widening active region and silicon waveguide to optimize optical confinement and increase saturation power. (b) Microscope image of the transfer-printed SOA on an E-beam rapid prototyping silicon sample. (c) SEM cross-sectional view of the taper tip and $\mu$ TP alignment markers. (d) Measured on-chip gain of 8.36 dB and output power versus increasing input power, leading to extraction of a saturation output power of 18.4                                                             | XXXIV |

| 7   | dBm, validating the tapered SOA as an effective booster amplifier. Demonstrators showcasing the versatility of the III-V-on-Si laser platform beyond telecom applications. (a) µLens-mounted laser PIC used for biomedical sensing via heartbeat monitoring through earlobe transmission. (b) Hybrid III-V-on-SiN laser achieving linewidths below 25 kHz for coherence-critical applications such as LiDAR. (c) Packaged SiPh laser with integrated wavelength monitoring and locking for gas sensing. (d) Programmable photonic chip with dynamic reconfiguration capabilities, illustrating the                                                           | XXXV  |

| 8   | adaptability of the integrated laser and amplifier platform Overgang van chipniveau naar waferniveau $\mu$ TP-integratie binnen de Transverse pilotlijn. (a) Overzicht van $\mu$ TP-integratie op waferschaal. (b) Demonstratie van $\mu$ TP-integratie op wafer-schaal van III-V-coupons op een 200 mm SiPh-wafer, met submicron uitlijningsprecisie en een printopbrengst van $100\%$                                                                                                                                                                                                                                                                      |       |

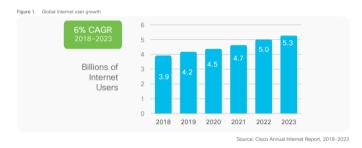

| 1.1 | Global Internet user growth (Cisco) [5]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 1-2   |

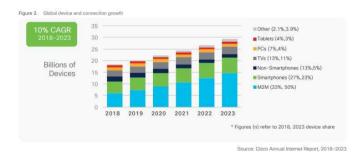

| 1.1 | Global device and connection growth (Cisco) [5]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 1-2   |

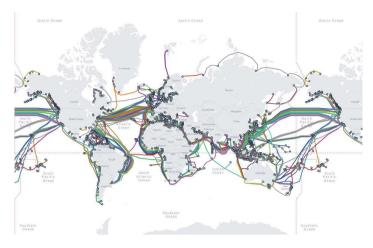

| 1.3 | Submarine optical fiber connections. Reproduced from [8]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |       |

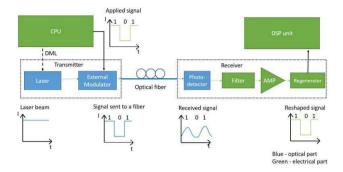

| 1.4  | Schematics of an optical communication link [12]                       | 1-4  |

|------|------------------------------------------------------------------------|------|

| 1.5  | Three levels of optical networks with different reach of the fibre-    |      |

|      | optic link. Reproduced from [13]                                       | 1-4  |

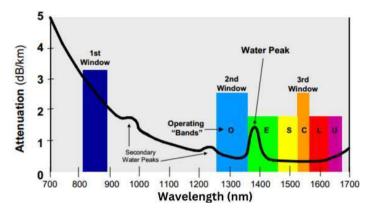

| 1.6  | Attenuation spectrum of optical fiber. Reproduced from [26]            | 1-5  |

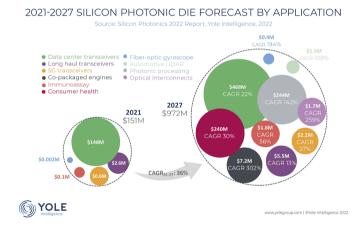

| 1.7  | Silicon photonic die forecast by application (Yole Group) [65]         | 1-8  |

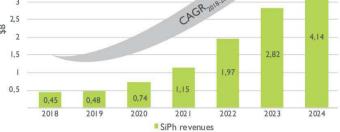

| 1.8  | Si Photonics-based transceiver forecast 2018-2024 (Yole Group)         |      |

|      | [68]                                                                   | 1-9  |

| 1.9  | Silicon photonics value chain for optical communication (Yole          |      |

|      | Group) [69]                                                            | 1-9  |

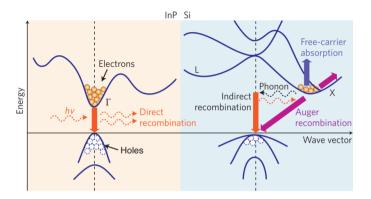

| 1.10 | Energy band diagrams and major carrier transition processes in         |      |

|      | InP (direct bandgap) and silicon crystals (indirect bandgap) [70]      | 1-10 |

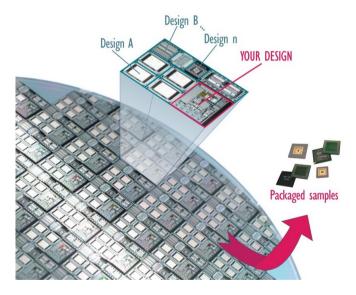

| 1.11 | Multi-project-wafer concept [71]                                       | 1-10 |

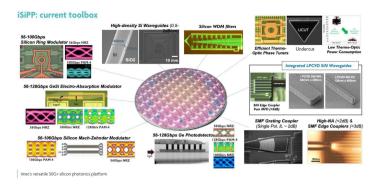

| 1.12 | Process Design Kit concept, imec iSiPP toolbox [72]                    | 1-11 |

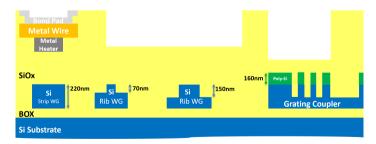

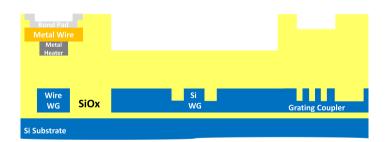

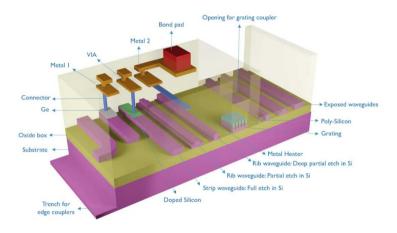

| 1.13 | IMEC Si-400 nm Platform (Size proportions are not preserved for        |      |

|      | illustrative clarity)                                                  | 1-12 |

| 1.14 | IMEC Passives+ platform (Size proportions are not preserved for        |      |

|      | illustrative clarity)                                                  | 1-12 |

| 1.15 | IMEC 400nm+ Platform (Size proportions are not preserved for           |      |

|      | illustrative clarity)                                                  | 1-13 |

|      | IMEC iSiPP50G Platform [74]                                            | 1-14 |

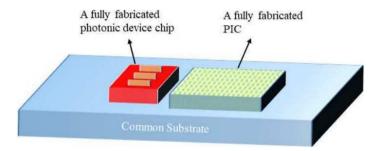

| 1.17 | A simple schematic of the hybrid integration technique. A gain         |      |

|      | chip is placed next to a Si PIC where both chips are mounted on a      |      |

|      | separate common substrate [19]                                         | 1-15 |

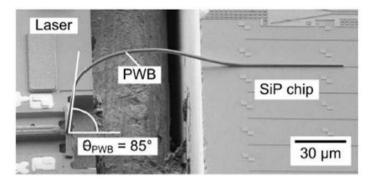

| 1.18 | A side-view SEM image of PWB, connecting an InP DFB laser              |      |

|      | chip to a waveguide on a SiP chip [84]                                 | 1-16 |

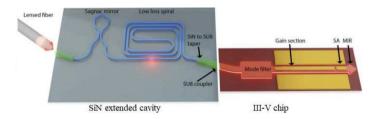

| 1.19 | Schematic view of a butt-coupled III-V chip to a SiN extended          |      |

|      | cavity [87]                                                            | 1-16 |

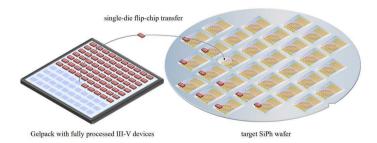

| 1.20 | Schematic view of flip-chip of a single device onto a SiPh wafer.      |      |

|      | Prior to the integration process, the devices are diced on the native  |      |

|      | substrate [97]                                                         | 1-17 |

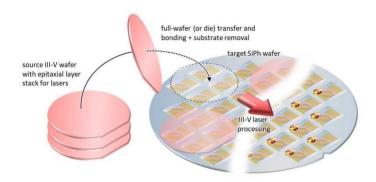

|      | Schematics of wafer bonding technology [12]                            | 1-18 |

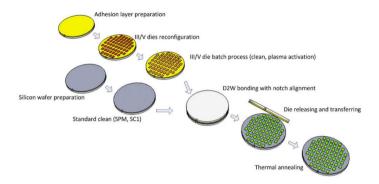

| 1.22 | Schematic process flow for multiple-die-to-wafer bonding. Repro-       |      |

|      | duced from [16, 106]                                                   | 1-19 |

| 1.23 | Schematic of Hetero-Epitaxial growth, where III-V materials such       | 4.20 |

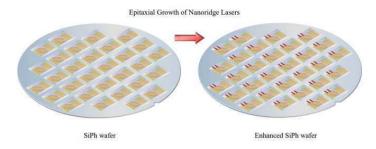

|      | as GaAs are grown as nanoridges on a silicon target wafer [97]         | 1-20 |

| 1.24 | Process flow schematic of regrowth on a bonding template III-V-        | 4.20 |

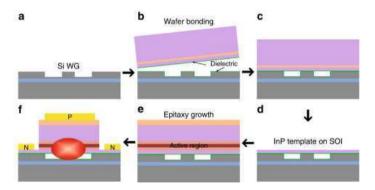

|      | on-Si integration [119]                                                | 1-20 |

| 1.25 | Schematic of $\mu$ TP-based integration in a parallel manner on 200    | 1 00 |

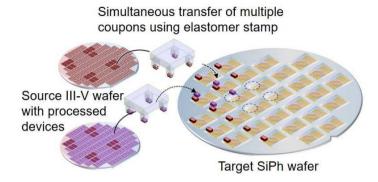

| 1.06 | mm or 300 mm Si photonic wafers [16]                                   | 1-22 |

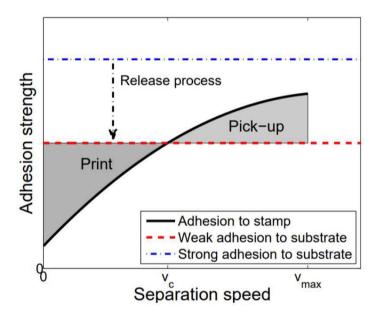

| 1.26 | Schematics of the separation energy dependencies on the peeling        |      |

|      | speed. When the peeling speed is lower than the critical speed         |      |

|      | printing will occur. When it is higher, pick-up will occur. Typ-       |      |

|      | ically, for inorganic semiconductor devices, the device-substrate      | 1 00 |

| 1 0- | separation energies are a lot higher (blue dashed-line) [12, 97, 129]. |      |

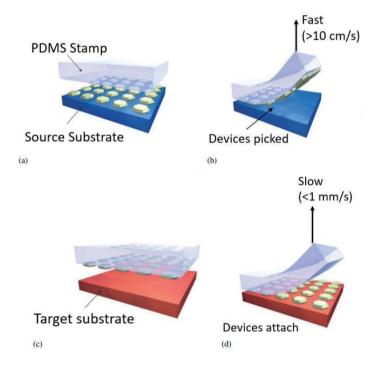

| 1.27 | The main concept of the transfer printing process [12, 124]            | 1-24 |

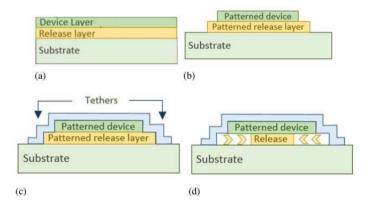

| 1.28 | Release process schematic [12, 131]                                                                                       | 1-25 |

|------|---------------------------------------------------------------------------------------------------------------------------|------|

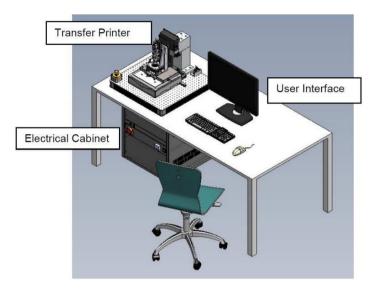

| 1.29 | The $\mu$ TP-100 system [132]                                                                                             | 1-26 |

| 1.30 | Schematics of the lab-scale transfer printing machine [132]                                                               | 1-26 |

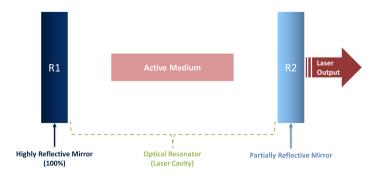

| 2.1  | Basic Schematic of a Laser                                                                                                | 2-6  |

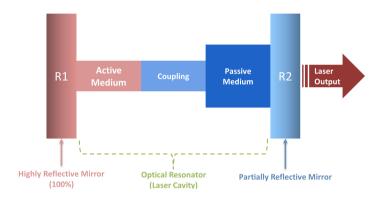

| 2.2  | Basic Schematic of a hybrid laser                                                                                         | 2-6  |

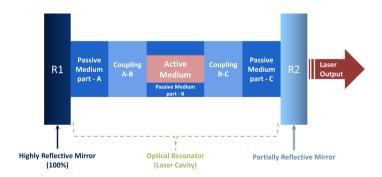

| 2.3  | Basic Schematic of a heterogeneous laser                                                                                  | 2-6  |

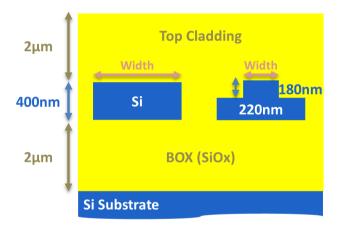

| 2.4  | Schematic cross-section of IMEC 400nm+ pltaform's WWG (left)                                                              |      |

|      | and RWG (right). The scale is not kept for a better representation.                                                       | 2-7  |

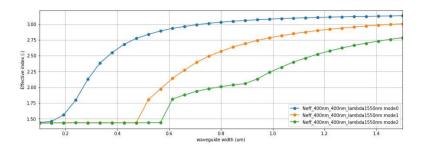

| 2.5  | Effective Index vs. the Core width of WWG at 1550 nm                                                                      | 2-8  |

| 2.6  | Effective Index vs. the Core width of RWG at 1550 nm                                                                      | 2-8  |

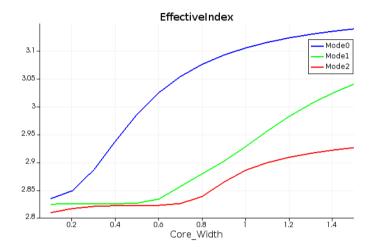

| 2.7  | Fundamental mode profile at 1550 nm with WWG width of 350                                                                 |      |

|      | nm (left), and 450 nm (right) to maximize the confinement in the                                                          |      |

|      | Si core or minimizing the sidewall loss                                                                                   | 2-8  |

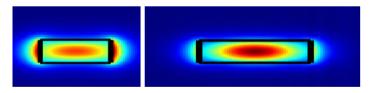

| 2.8  | (a): Measured transmission spectra for a set of waveguides with                                                           |      |

|      | different length, (b): Calculated propagation loss of the fundamen-                                                       |      |

|      | tal TE mode in 650 nm wide rib waveguide [15]                                                                             | 2-9  |

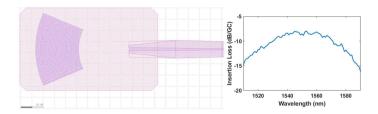

| 2.9  | The screenshot of the GDS layout of the IMEC 400nm+ PDK grat-                                                             |      |

|      | ing coupler (left), and it's insertion loss spectrum (right)                                                              | 2-10 |

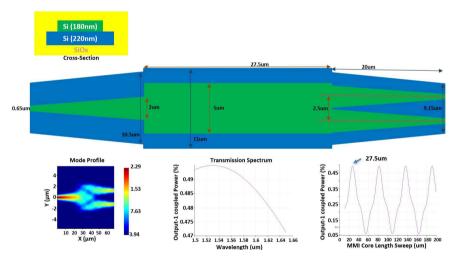

| 2.10 | The schematic layout design of the 50/50 1x2 MMI based on IMEC                                                            |      |

|      | 400nm+ RWG, The mode profile, transmission spectrum, and cou-                                                             |      |

|      | pling percentage vs. the core length of the MMI                                                                           | 2-10 |

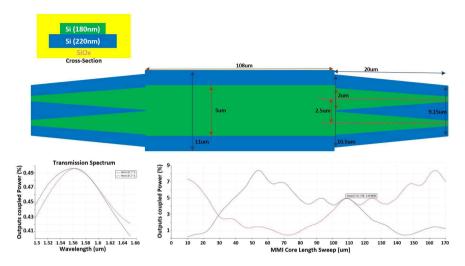

| 2.11 | The schematic layout design of the 50/50 2x2 MMI based on IMEC                                                            |      |

|      | 400nm+ RWG, transmission spectrum and coupling percentage vs.                                                             |      |

|      | the core length of the MMI                                                                                                | 2-11 |

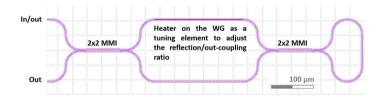

| 2.12 | Schematic layout of a tunable Sagnac loop mirror formed by con-                                                           |      |

|      | necting two 50/50 MMIs. In the default state (no phase shift), the                                                        |      |

|      | structure reflects all input light back to the input waveguide due to                                                     |      |

|      | destructive interference at the output. By applying a phase shift                                                         |      |

|      | via a heater on one of the MZI arms, the reflection/out-coupling                                                          |      |

|      | ratio can be tuned. The tuning range spans from 0% to 100% out-                                                           | 2 11 |

| 2 12 | coupling.                                                                                                                 | 2-11 |

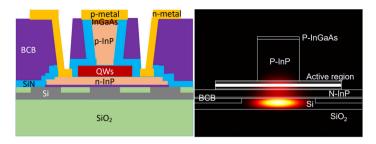

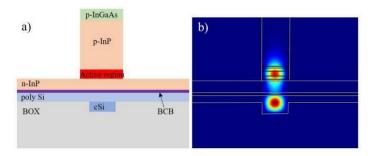

| 2.13 | Schematic layout of a cross-section of the III-V-on-Si laser (left),                                                      |      |

|      | and the intensity profile of the fundamental optical mode in the                                                          | 2 12 |

| 2 14 | hybrid III-V/Si waveguide (right) [15]                                                                                    | 2-13 |

| 2.14 | ture [15]                                                                                                                 | 2-13 |

| 2 15 |                                                                                                                           | 2-13 |

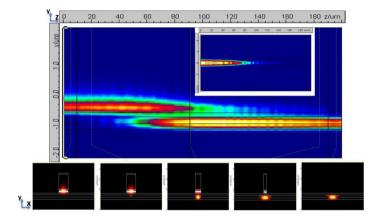

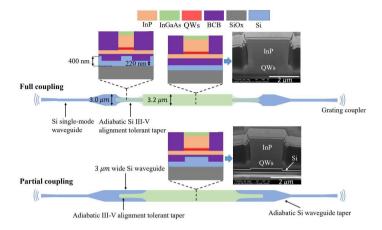

| 2.13 | Schematics and FIB cross-sections illustrating the design of the full-coupling and partial-coupling III-V-on-Si SOAs [23] | 2-14 |

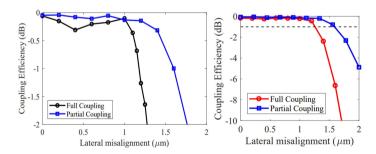

| 2 16 | The simulated coupling efficiency of the adiabatic taper structures                                                       | 211  |

| 2.10 | for the partial and full-coupling designs versus the lateral misalign-                                                    |      |

|      | ment: Si-400 nm (left), iSiPP50G (right) [23]                                                                             | 2-14 |

| 2.17 | Schematic illustration and simulated mode profile of the ISIPP50G                                                         |      |

|      | waveguide cross-section with integrated SOA [23]                                                                          | 2-15 |

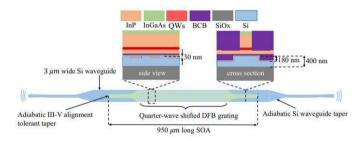

| 2.18  | Schematic illustrating the design of the DFB laser, the cross-section                                                             |       |

|-------|-----------------------------------------------------------------------------------------------------------------------------------|-------|

|       | view of the adiabatic taper and the side view of the DFB grating [23]                                                             | .2-15 |

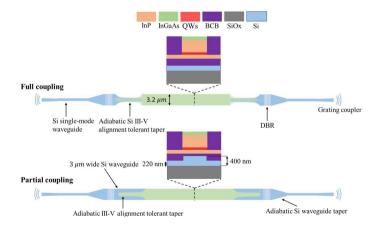

| 2.19  | Design schematic of full-coupling and partial-coupling DBR lasers.                                                                |       |

|       | The cross-section in the gain section is also illustrated [23]                                                                    | 2-15  |

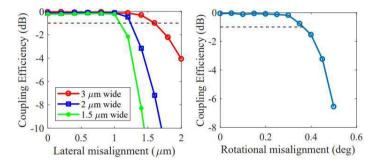

| 2.20  | (left) Calculated power coupling between full-coupling III-V adi-                                                                 |       |

|       | abatic taper design and Si waveguide of width 3.0 $\mu$ m, 2.0 $\mu$ m                                                            |       |

|       | and 1.5 $\mu$ m, (right) Calculated coupling efficiency against the ro-                                                           |       |

|       | tational misalignment between III-V adiabatic taper and Si waveg-                                                                 |       |

|       | uide [23]                                                                                                                         | 2-16  |

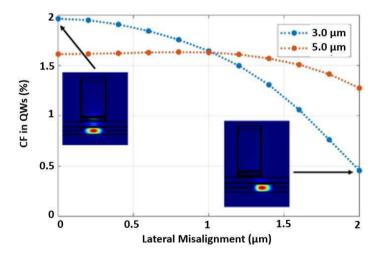

| 2.21  | The change in confinement factor in QWs with the misalignment                                                                     | 2-10  |

| ∠.∠ı  | variation for 3.0 $\mu$ m and 5.0 $\mu$ m Si waveguide width, insets illus-                                                       |       |

|       | , ,                                                                                                                               | 2 16  |

|       | trate the mode profile at zero and 2.0 $\mu$ m misalignment [23]                                                                  | 2-16  |

| 2.22  | (a) Calculated coupling efficiency for variation in a) adiabatic III-                                                             |       |

|       | V taper width, (b) n-InP thickness, (c) QW width and (d) BCB                                                                      |       |

|       | thickness [23]                                                                                                                    | 2-17  |

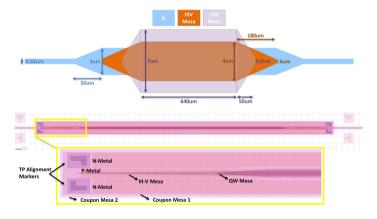

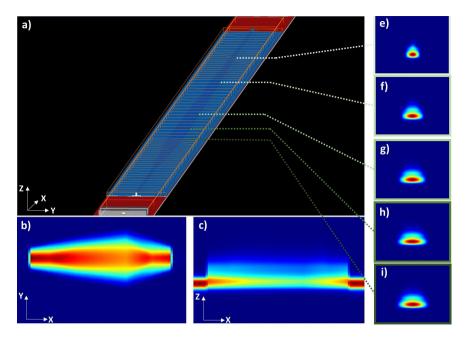

|       | Schematic (Top) and layout design (Bottom) of this work's SOA. $\ .$                                                              | 2-17  |

| 2.24  | Simulated optical coupling from the III–V to silicon. (a) Optical                                                                 |       |

|       | intensity distribution showing mode coupling between the silicon                                                                  |       |

|       | waveguide and III–V layers. (b) Impact of $\mu$ TP misalignment on                                                                |       |

|       | mode confinement and transmission efficiency [27]                                                                                 | 2-18  |

| 2.25  | Schematic (Top) and layout design (Bottom) of this work's SOA                                                                     | 2-19  |

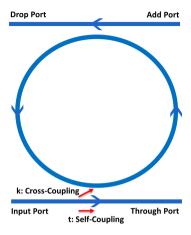

| 2.26  | Schematic of an add-drop ring resonator with two bus waveguides                                                                   |       |

|       | and a ring waveguide                                                                                                              | 2-21  |

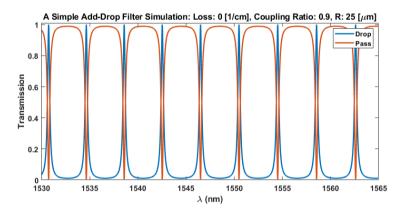

| 2.27  | Transmission to the through port and drop port of an add-drop ring                                                                |       |

|       | resonator, as a function of wavelength                                                                                            | 2-22  |

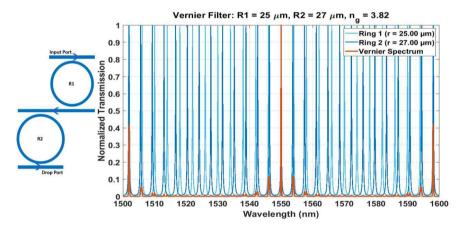

| 2.28  | Vernier filter schematic (left), Transmission to the drop port of the                                                             |       |

|       | vernier filter, as a function of wavelength                                                                                       | 2-23  |

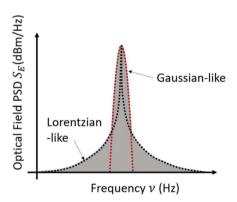

| 2.29  | The spectral line shape of the laser optical field exhibits a Gaussian-                                                           |       |

|       | like profile near the peak and transitions to a Lorentzian-like pro-                                                              |       |

|       | file at the tails. Axes are presented in logarithmic scale. Represen-                                                             |       |

|       | tation from [38]                                                                                                                  | 2-24  |

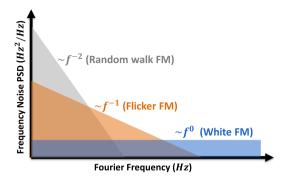

| 2.30  |                                                                                                                                   |       |

|       | quency noise as a function of Fourier frequency, highlighting the                                                                 |       |

|       | various noise contributions typically present in hybrid-integrated                                                                |       |

|       | diode lasers, each indicated with different colors [28, 38]                                                                       | 2-26  |

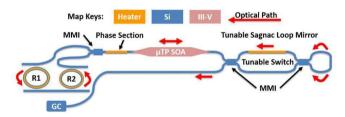

| 2.31  |                                                                                                                                   |       |

| 2.31  | able narrow-linewidth III-V-on-Si laser.                                                                                          | 2-27  |

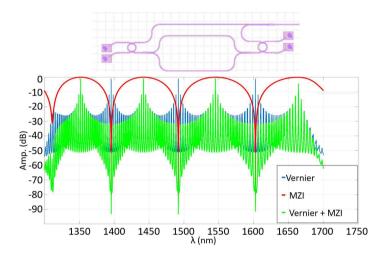

| 2 3 2 | An MZI added in series to a Vernier filter to double the total FSR.                                                               | 2-21  |

| 2.32  | In this configuration, the arm's length difference of MZI needs to                                                                |       |

|       | be chosen so the MZI's FSR be twice the Vernier's FSR                                                                             | 2 20  |

| 22    |                                                                                                                                   | 2-30  |

| 2.33  | 3D schematic layout of the dual-laser configuration. For simplicity, just one pair of electrical compactions to a heater is shown | 2 21  |

| 24    | ity, just one pair of electrical connections to a heater is shown                                                                 | 2-31  |

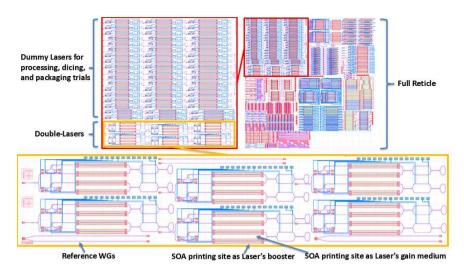

| 2.34  | Dual-Laser GDS Mask                                                                                                               | 2-32  |

| 2.35  |                                                                                                                                   | 2 22  |

|       | grated metal layers and back-end stack                                                                                            | 2-33  |

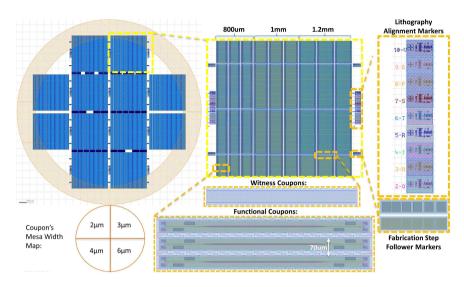

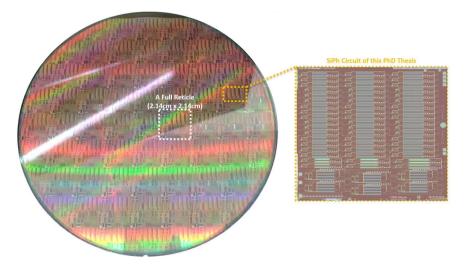

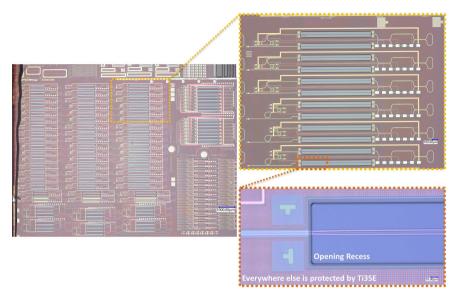

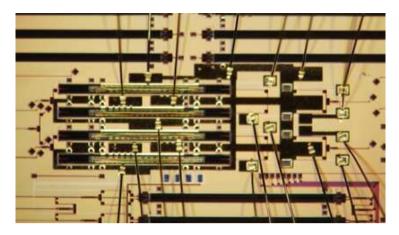

| 2.36 | Fabricated design on a 200 mm SiPh wafer based on the IMEC 400nm+ platform through an internal MPW run                                                                                                                              | 2-33 |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| 2.37 | Opening recess patterning by photolithography using Ti35E photoresist.                                                                                                                                                              | 2-34 |

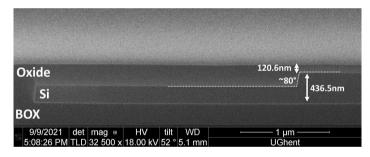

| 2.38 | Cross-sectional SEM image of the waveguide inside a recess after back-end etch-back by RIE                                                                                                                                          | 2-34 |

| 2.39 | Microscope image of the over-etched Si-waveguide inside a recess after back-end etch-back by RIE                                                                                                                                    | 2-34 |

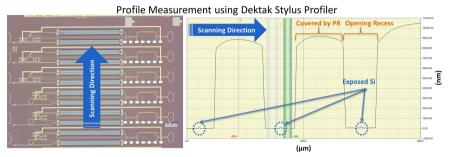

| 2.40 | Schematic cross-section overview after completion of back-end recess opening by BHF etching (top). Microscope image of the processed sample and its scanned profile (bottom), showing the Si-waveguide is exposed after BHF etching | 2-35 |

| 2.41 | Schematic cross-section overview after BCB spray-coating over the recess                                                                                                                                                            | 2-35 |

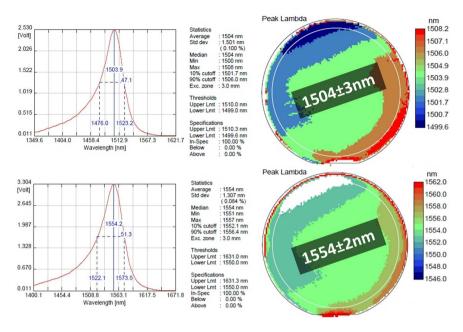

| 2.42 | Photoluminescence spectra and wafer map of the III-V SOA epitaxial layer stacks with MQW variants, achieving photoluminescence peaks at 1500 nm and 1550 nm, reported by III-V Lab                                                  | 2-37 |

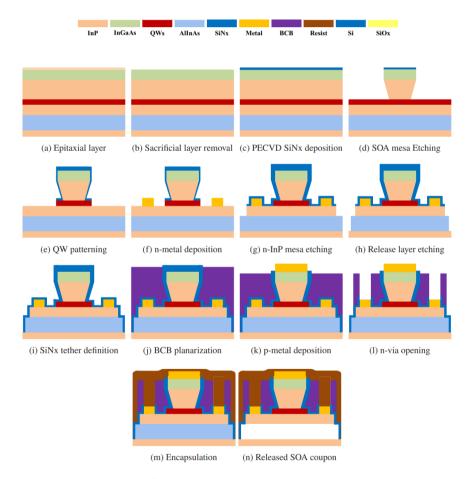

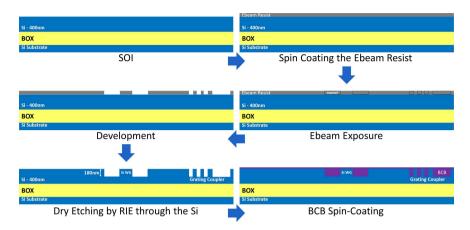

| 2.43 | Process flow of SOA device fabrication on the source InP substrate.                                                                                                                                                                 | 2-38 |

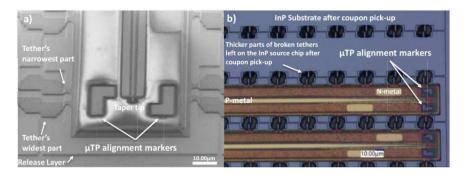

| 2.44 | A fabricated InP coupon source: a) Side-view SEM image, b) Top-view microscope image.                                                                                                                                               | 2-39 |

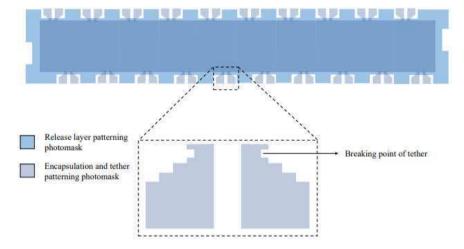

| 2.45 | Schematic presentation of the photomask used for patterning the release layer and encapsulating the device, along with a close-up view of the tether design [23]                                                                    | 2-39 |

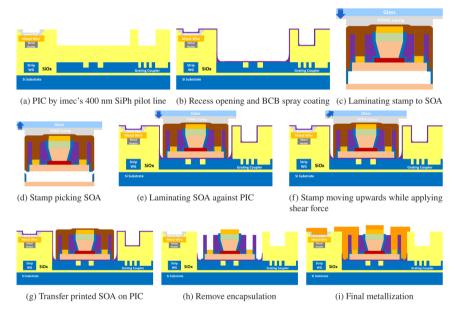

| 2.46 | Process flow of PIC preparation for $\mu$ TP, micro-transfer printing and post processing                                                                                                                                           | 2-40 |

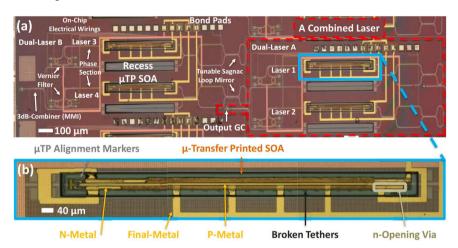

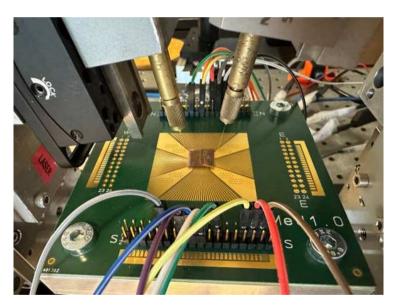

| 2.47 | (a) Stitched microscope image of the combined widely tunable lasers. (b) Micro-transfer-printed III-V amplifier in the recess (after final metallization).                                                                          | 2-41 |

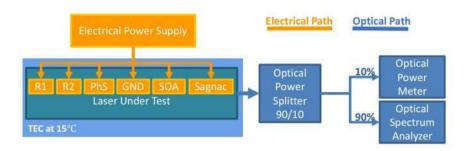

| 2.48 | Schematic layout of the laser characterization setup                                                                                                                                                                                | 2-42 |

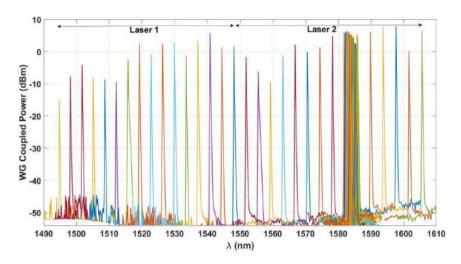

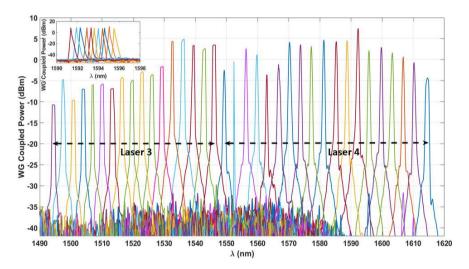

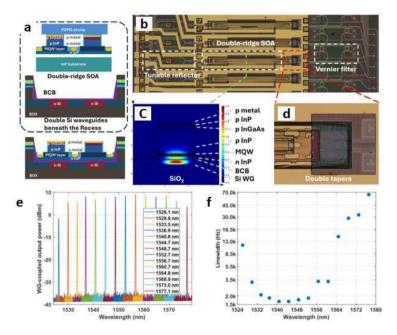

| 2.49 | Tuning spectrum of Dual-Laser A (300 nm ring gap). Fine tuning in steps of 100 pm was performed over a 4 nm range, equivalent to the FSR of one ring.                                                                               | 2-43 |

| 2.50 | Tuning spectrum of Dual-Laser B (200 nm ring gap). Fine tuning was done in 10 steps over a 4 nm range, matching the ring FSR                                                                                                        | 2-43 |

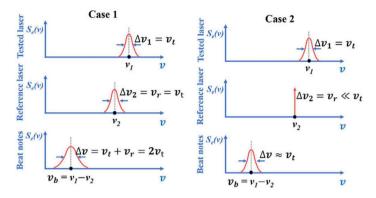

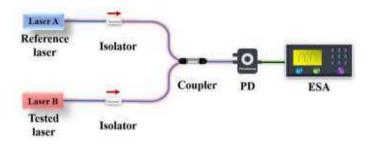

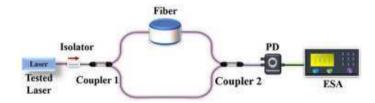

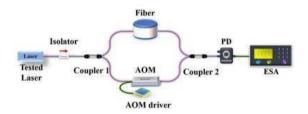

| 2.51 | Principle of optical beat notes [49]                                                                                                                                                                                                | 2-45 |

| 2.52 | Beat note with a reference laser [49]                                                                                                                                                                                               | 2-45 |

| 2.53 | Delayed self-homodyne detection [49]                                                                                                                                                                                                | 2-46 |

| 2.54 | Delayed self-heterodyne detection [49]                                                                                                                                                                                              | 2-46 |

| 2.55 | OEwaves HI-Q® LASER LINEWIDTH/PHASE NOISE ANA-<br>LYZER [57, 59]                                                                                                                                                                    | 2-47 |

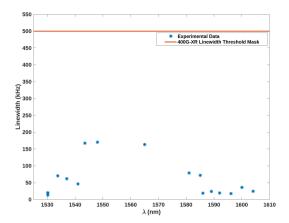

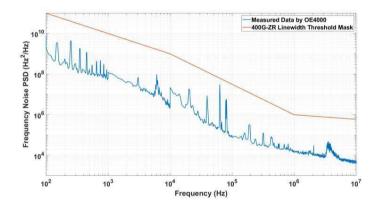

| 2.36 | Measured Lorentzian linewidth of the Dual-Laser A (ring gap = 300 nm) across its tuning range, obtained using the OEwaves OE4000 Optical Phase Noise Test System. All measured linewidths remain well below the 400G-ZR standard linewidth threshold mask (500 kHz), demonstrating the laser's suitability for advanced coherent applications                     | 2-48 |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| 2.57 | Frequency noise power spectral density of Laser 1 (ring gap = 300 nm), measured using the OEwaves OE4000 Optical Phase Noise Test System. The laser was biased at 120 mA and operated at a wavelength of 1530 nm. The measured noise remains well below the 400G-ZR linewidth threshold mask, indicating suitability for coherent optical communication standards | 2-48 |

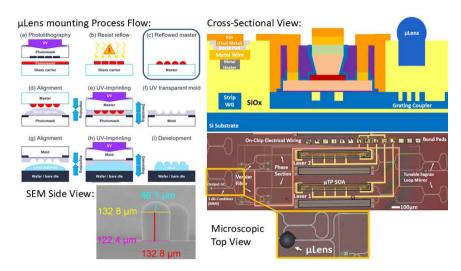

| 2.58 | $\mu$ Lens mounting process flow by CSEM (Top Left) [67], along with the schematic cross-section view of the PIC with a microtransfer-printed laser and a $\mu$ Lens (Top Right). Microscope top view image of the mounted $\mu$ Lens on a PIC (Bottom Right), with a side view SEM image (Bottom Left)                                                           | 2-51 |

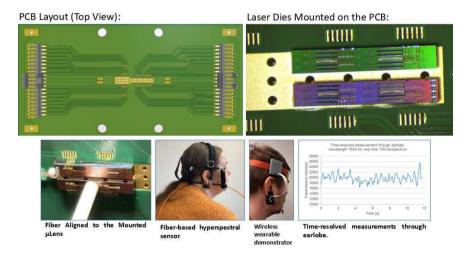

| 2.59 | PCB layout by VTT (Top Left). Two Laser dies mounted and wirebonded to the PCB (Top Right). Two prototype configurations as fiber-based and wireless wearable Hyperspectral sensors with the time-resolved measurements of heartbeat through the earlobe                                                                                                          | 2-51 |

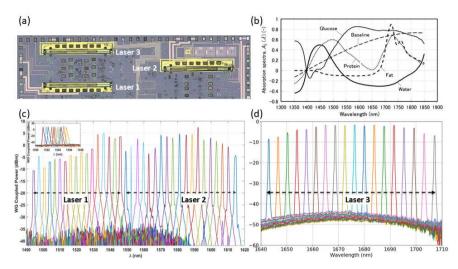

| 2.60 | (a) Microscope image of the PIC with three $\mu$ TP lasers. (b) Absorption peak of biological substances [71]. (c) Previously demonstrated tuning spectrum within the range of 1500-1600 nm [72]. (d) Extended tunability range of more than 60 nm within the range of 1640-1710 nm [27]                                                                          | 2-53 |

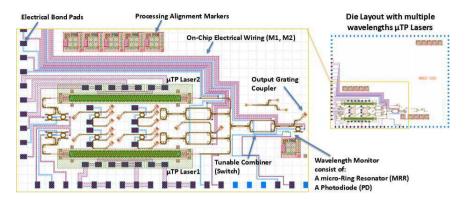

| 2.61 | Schematic layout of a SiPh PIC integrating two $\mu$ TP-based lasers, a tunable optical switch (combiner), and a wavelength monitoring and locking system composed of a micro-ring resonator (MRR) and a photodiode (PD)                                                                                                                                          | 2-54 |

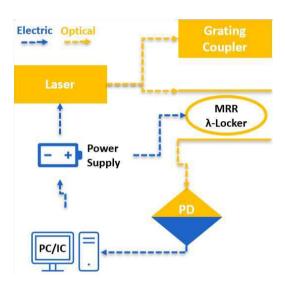

| 2.62 | Block diagram illustrating the concept of the on-chip wavelength monitoring and locking system. A portion of the laser output is coupled to an MRR whose resonance is swept via a heater. When the MRR's resonance matches the laser wavelength, the signal is dropped to the PD and converted into an electrical signal for feedback control.                    | 2-54 |

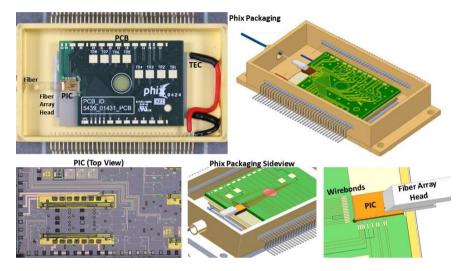

| 2.63 | Packaged SiPh laser PIC using PHIX assembly technology. The 3D schematic illustrates the alignment of the fiber array (FA) to the PIC while the chip is wirebonded to the PCB. The microscope image shows the PIC surface, including gold metallization atop the SOA regions to redistribute electrical connections to the bond pads.                             | 2-55 |

| 2.64 | Narrow-Linewidth III–V/SiN laser [81]. (a) Taper design with simulated mode evolution from SiN to InP. (b) Photonic circuit with $\mu$ TP-integrated gain, tunable Sagnac loop mirror, MRRs, and                                                                                                                                                                                                                                                                                                                                                 |             |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

|      | phase control. (c) Output spectrum showing 54 nm tuning range. (d) Linewidths <25 kHz across the wavelength tuning range, suitable for coherence-critical applications                                                                                                                                                                                                                                                                                                                                                                           | 2-56        |

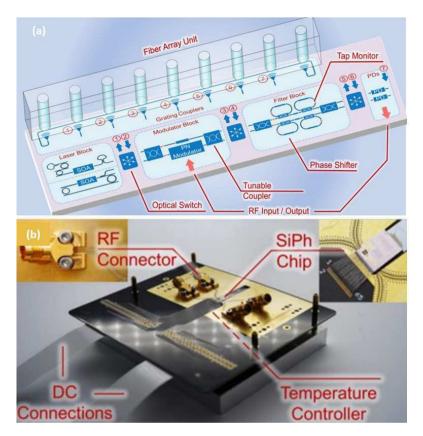

| 2.65 | photonic engine, highlighting its modular building blocks: $\mu$ TP-integrated lasers and SOAs, high-speed modulators, optical switches, tunable couplers, phase shifters, and tap monitors, all interfaced via a fiber array unit. (b) Packaged photonic engine mounted on a                                                                                                                                                                                                                                                                    |             |

|      | PCB with integrated DC, RF, and thermal control interfaces. The SiPh chip, containing all active and passive components, is wire-bonded for external interfacing and control [82]                                                                                                                                                                                                                                                                                                                                                                | 2-58        |

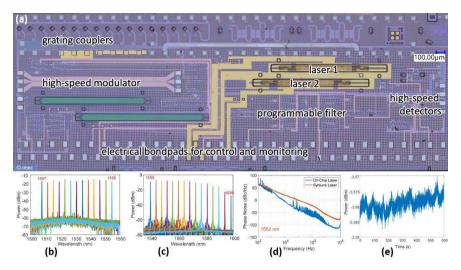

| 2.66 | (a) Microscope image of the fabricated iSiPP50G photonic engine chip with labeled components: $\mu$ TP-integrated tunable lasers, SOAs, high-speed modulators, programmable filter, detectors, and grating couplers. (b–c) Optical spectra demonstrating wide tunability of the on-chip lasers across 1507–1598 nm. (d) Phase noise comparison between the $\mu$ TP laser and a commercial Syntune laser, showing competitive noise performance. (e) Time-domain power stability trace of the $\mu$ TP-integrated laser output, confirming suit- |             |

|      | ability for coherent signal processing applications [82]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 2-59        |

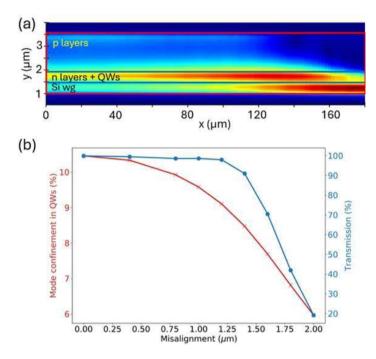

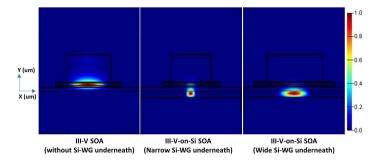

| 3.1  | A comparison of optical mode profile confinement in the QWs of SOAs based on III-V and hybrid III-V-on-Si structures. By incorporating the underlying Si waveguide and making it wider, the confinement in the QWs reduces as the mode gets pushed down into the Si waveguide                                                                                                                                                                                                                                                                    | 3-5         |

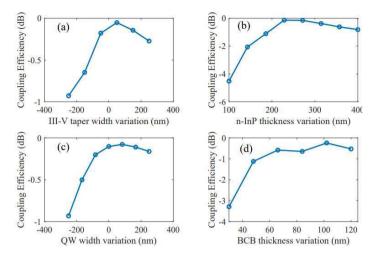

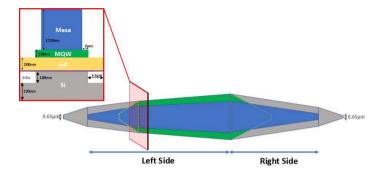

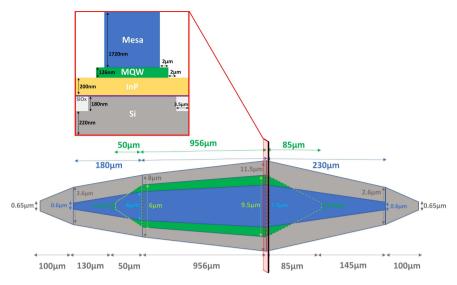

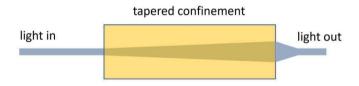

| 3.2  | The proposed tapering scheme for the III-V-on-Si integrated SOA to increase the optical saturation power level, while maintaining                                                                                                                                                                                                                                                                                                                                                                                                                |             |

| 3.3  | enough optical gain                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 3-6         |

| 3.4  | ing the tolerance to lateral misalignment                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 3-7         |

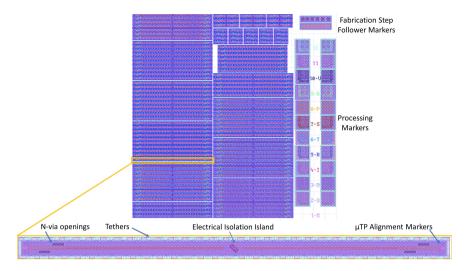

| 3.5  | The GDS mask prepared for the fabrication of the proposed InP-based SOA coupons.                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 3-9         |

|      | oubca 5 021 coupons                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | <b>シ</b> ーク |

| 3.6  | The GDS mask prepared for patterning the Si waveguide circuits                           | 2.0  |

|------|------------------------------------------------------------------------------------------|------|

| 2.7  | by e-beam lithography                                                                    | 3-9  |

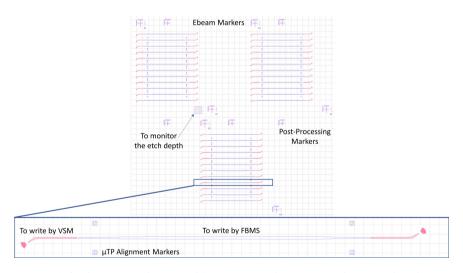

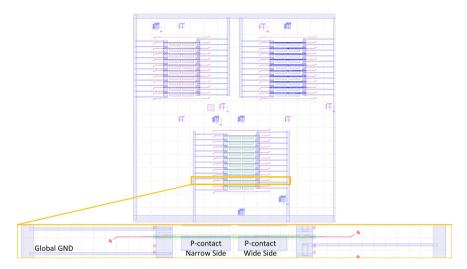

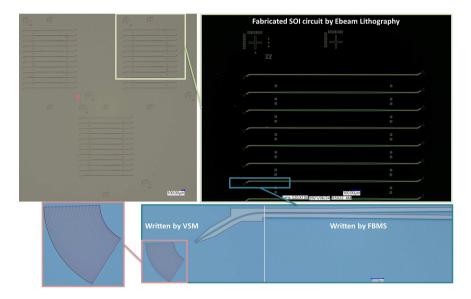

| 3.7  | The GDS mask showing the InP based SOA coupon on top of the                              | 3-10 |

| 3.8  | Si waveguide with the final metal on top                                                 | 3-10 |

|      | The microscope image of the fabricated waveguide circuit                                 |      |

| 3.9  |                                                                                          |      |

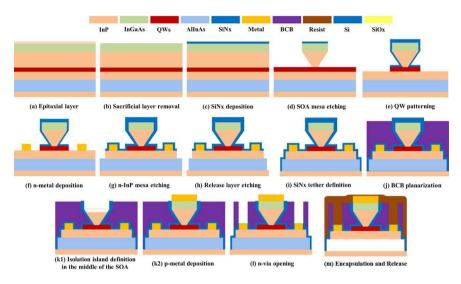

| 3.10 | InP-based SOA coupon fabrication steps.                                                  | 3-12 |

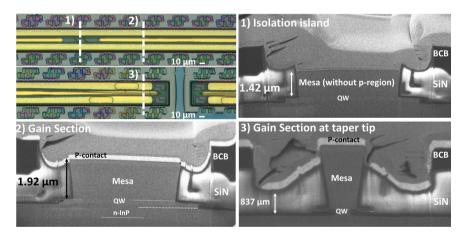

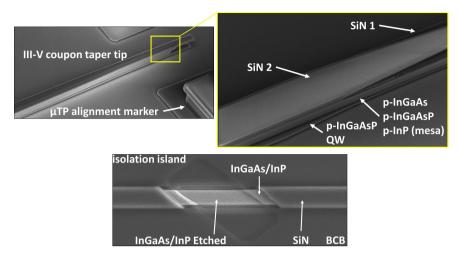

| 3.11 | FIB cross-section images of the fabricated InP SOA coupons. Places                       |      |

|      | where the FIB images were taken are marked on the top left mi-                           | 2 12 |

| 2 12 | croscope image which shows a top-view of the SOA coupons                                 | 3-12 |

| 3.12 | Side view SEM images of the taper and the electrical isolation island of the SOA coupons | 3-13 |

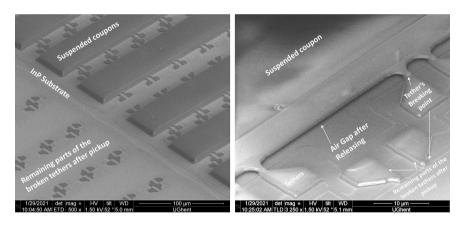

| 3.13 | Side view SEM images of the encapsulated SOA coupons after                               |      |

|      | release, showing the suspended coupons on their tethers as well as                       |      |

|      | the breakage point of the remaining tethers after pickup                                 | 3-13 |

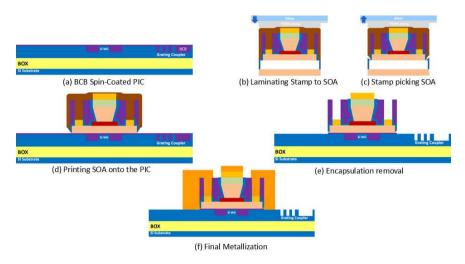

| 3.14 | Process flow of micro-transfer printing and post processing                              | 3-14 |

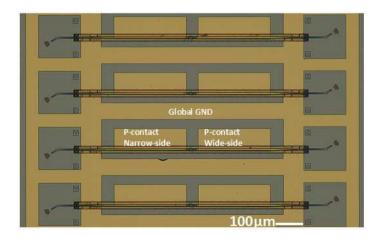

|      | Microscope image of a printed SOA coupon on the Si waveguide.                            | 3-14 |

|      | Microscope image of a printed array of SOA coupons on the SiPh                           |      |

|      | chip with the final metallization on top to complete the circuit                         | 3-14 |

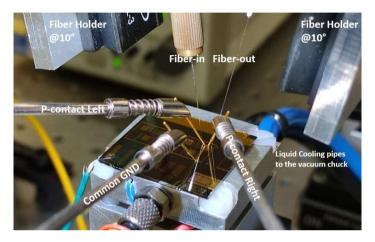

| 3.17 | Measurement setup of the integrated high saturation power SOA                            | 3-15 |

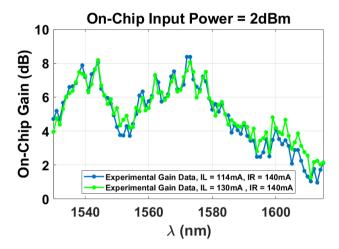

|      | On-chip gain as a function of wavelength, while the waveguide-                           |      |

|      | coupled input power is 2.0 dBm and the pump currents of the left                         |      |

|      | and right sides are 114/130 mA and 140 mA, respectively                                  | 3-16 |

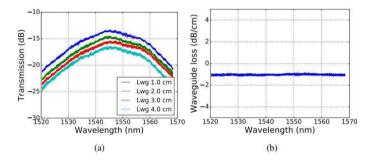

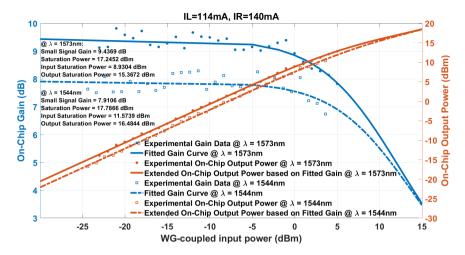

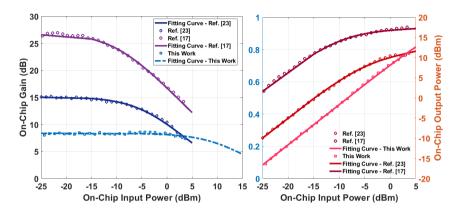

| 3.19 | The gain as a function of on-chip optical input power (left side).                       |      |

|      | The on-chip output power as a function of the input power (right                         |      |

|      | side). The points are measured values, the lines are fitted curves.                      |      |

|      | The pump currents of the left and right sides are 114 mA and 140                         |      |

|      | mA, respectively                                                                         | 3-17 |

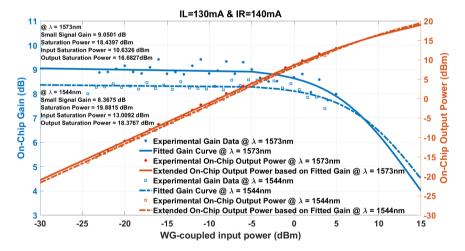

| 3.20 | The gain as a function of on-chip optical input power (left side).                       |      |

|      | The on-chip output power as a function of the input power (right                         |      |

|      | side). The points are measured values, the lines are fitted curves.                      |      |

|      | The pump currents of the left and right sides are 130 mA and 140                         |      |

|      | mA, respectively                                                                         | 3-17 |

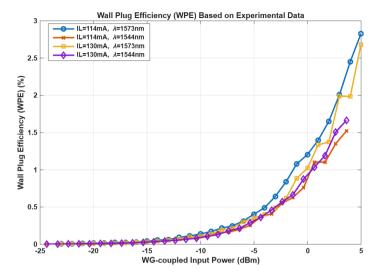

| 3.21 | The measured wall-plug efficiency of the SOAs as a function of                           |      |

|      | the on-chip optical input power                                                          | 3-18 |

| 3.22 | Comparison of this work against state of the art references [17, 23].                    |      |

|      | The gain as a function of on-chip optical input power (left side).                       |      |

|      | The on-chip output power as a function of the input power (right                         |      |

|      | , 1                                                                                      | 3-19 |

| 3.23 | $\varepsilon$                                                                            |      |

|      | pered silicon waveguide. Transitions between the silicon and hy-                         |      |

|      | brid waveguides, which are not shown here, are designed to be                            |      |

|      | adiabatic. At the output, the wider silicon waveguide is gradually                       | 2.20 |

|      | tapered back to a single-mode waveguide [14]                                             | 3-20 |

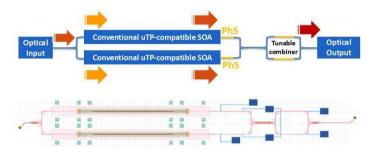

| 3.24       | Schematic illustration of the coherent beam combining SOA configuration (top). Screenshot of the GDS layout of the proposed            |      |

|------------|----------------------------------------------------------------------------------------------------------------------------------------|------|

| 2 25       | III-V-on-Si integrated circuit (bottom)                                                                                                | 3-21 |

|            | combining SOA configuration to PCB                                                                                                     | 3-22 |

|            | Wire-bonded sample of coherent beam combining SOA configuration to PCB on a measurement setup                                          | 3-22 |

| 3.27       | Double-Ridge SOA configuration, providing the laser's gain and booster SOAs into a single encapsulated coupon [31]                     | 3-23 |

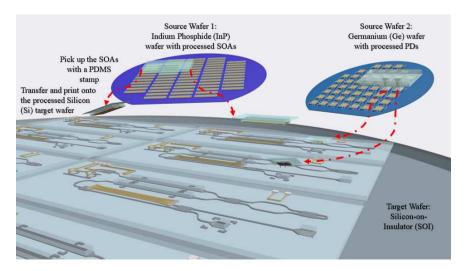

| 4.1<br>4.2 | Wafer-scale $\mu$ TP integration schematic                                                                                             | 4-2  |

| 4.2        | vice value chain and initial industrial manufacturing capabilities, providing a path to scalable high-volume manufacturing for inno-   |      |

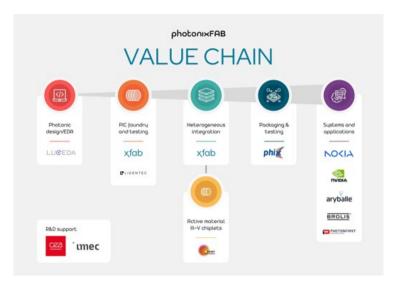

| 4.2        | vative product developers [4]                                                                                                          | 4-4  |

| 4.3        | EVG®101 spray coater installed at Ghent University cleanroom for wafer-scale thin-film BCB deposition                                  | 4-5  |

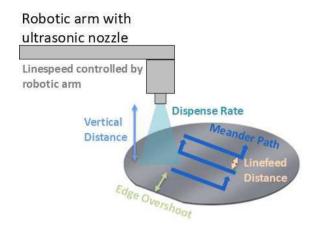

| 4.4        | Spray coating scheme, mentioning the important controllable parameters of EVG101                                                       | 4-6  |

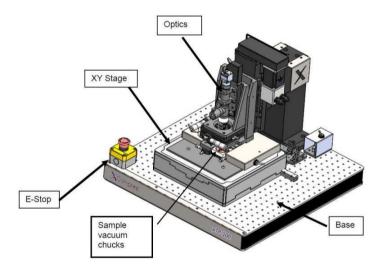

| 4.5        | ASMPT Amicra Nano printer installed at Ghent University Clean-                                                                         |      |

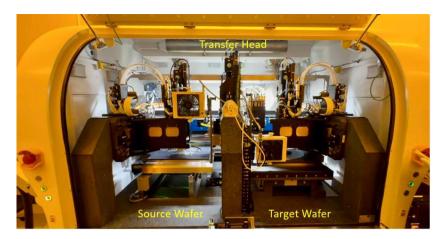

| 4.6        | room for wafer-scale $\mu$ TP                                                                                                          | 4-7  |

|            | chuck, target chuck, and the transfer head                                                                                             | 4-8  |

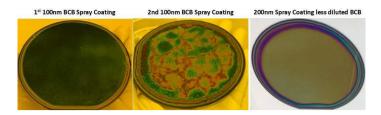

| 4.7        | (Left) 1st layer of 100 nm BCB spray coated on a blank Si wafer, (Middle) 2nd layer of 100 nm BCB spray coated on the same wafer       |      |

|            | to reach 200 nm of BCB in total. (Right) One time of spray coating                                                                     |      |

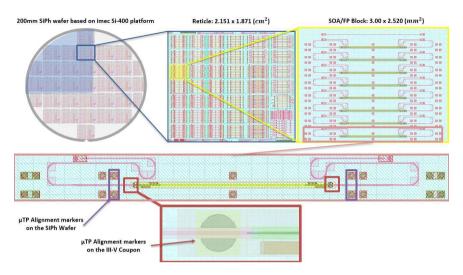

| 4.8        | less diluted BCB on a blank Si wafer to reach 200 nm of thickness. Full layout of the 200 mm SiPh wafer, highlighting a zoomed-        | 4-10 |

|            | in view of a representative reticle used for $\mu TP$ integration. Each                                                                |      |

|            | block within the reticle consists of standardized SOA/FP laser building blocks from the $\mu$ TP-PDK, featuring tunable design parame- |      |

|            | ters such as cavity and coupon lengths, waveguide bend radius,                                                                         |      |

|            | and directional coupler splitting ratio, configurable for both C-                                                                      | 1 11 |

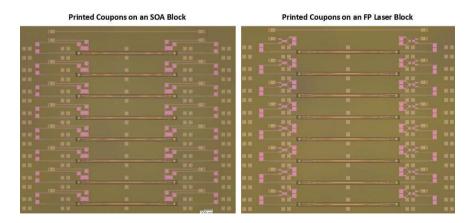

| 4.9        | band and O-band operation                                                                                                              | 4-11 |

| 1.7        | wafer-scale printer                                                                                                                    | 4-11 |

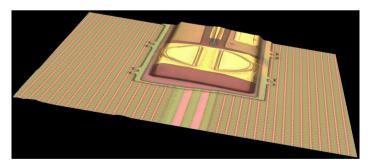

| 4.10       | The 3D optical microscope reconstruction of an InP SOA coupon                                                                          |      |

|            | printed on a Si waveguide using a wafer-scale printer, showing the                                                                     | 4 10 |

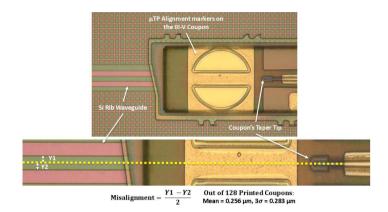

| 4.11       | sub-micron alignment precision                                                                                                         | 4-12 |

| 7.11       | on the coupons to ensure high alignment precision. A zoomed-in                                                                         |      |

|            | view, illustrating the way of lateral misalignment measurement                                                                         | 4-13 |

### List of Tables

| 1.1 | Various waveguide platforms, advantages and disadvantages                                              | 1-7  |

|-----|--------------------------------------------------------------------------------------------------------|------|

| 2.1 | Integrated laser's requirements extracted from the optical specifications of a 400G-ZR transmitter [6] | 2-4  |

| 2.2 | IMEC 400nm+ RWG specifications extracted from the simulations                                          |      |

|     | and measurements                                                                                       | 2-9  |

| 2.3 | C-band microring resonator parameters                                                                  | 2-28 |

| 2.4 | L-band microring resonator parameters                                                                  | 2-28 |

| 2.5 | Relationship between the gap of the constituent rings and the es-                                      |      |

|     | timated Vernier Q-factor and Vernier Linewidth Reduction Factor                                        |      |

|     | (LRF) for C-band and L-band                                                                            | 2-29 |

| 2.6 | III-V SOA epitaxial layer stacks, with MQW variants achieving                                          |      |

|     | photoluminescence peaks at 1500 nm and 1550 nm                                                         | 2-36 |

| 2.7 | Comparison of key performance metrics for widely tunable narrow-                                       |      |

|     | linewidth integrated lasers                                                                            | 2-49 |

| 3.1 | Comparison of Hybrid III-V-on-Si SOAs                                                                  | 3-19 |

### List of Acronyms

A

ADC Analog-to-Digital Converter AWG Arrayed Waveguide Grating

B

BER Bit Error Rate

$\mathbf{C}$

C-Band Conventional Band (1530–1565 nm)

CMOS Complementary Metal-Oxide-Semiconductor

CW Continuous Wave

D

DBR Distributed Bragg Reflector

DFB Distributed Feedback

DSP Digital Signal Processing

DUT Device Under Test

$\mathbf{E}$

EDA Electronic Design Automation

EDFA Erbium-Doped Fiber Amplifier

EPFL École Polytechnique Fédérale de Lausanne

EPI Epitaxial Layer

F

FBG Fiber Bragg Grating

FP Fabry-Pérot

FMCW Frequency-Modulated Continuous-Wave

FSR Free Spectral Range

FWHM Full Width at Half Maximum

G

GC Grating Coupler GBW Gain Bandwidth

I

III–V Compound semiconductors from group III and V

IL Insertion Loss

IMEC Interuniversity Microelectronics Centre

InP Indium Phosphide

L

LASER Light Amplification by Stimulated Emission of Radi-

ation

LiDAR Light Detection and Ranging L-Band Long Band (1565–1625 nm)

M

MFD Mode Field Diameter

MIR Mid-Infrared

$\begin{array}{ll} \text{MRR} & \text{Microring Resonator} \\ \mu\text{TP} & \text{Micro-Transfer Printing} \\ \text{MZI} & \text{Mach-Zehnder Interferometer} \end{array}$

### N

n-InP n-doped Indium Phosphide NRZ Non-Return-to-Zero

### O

OE Optoelectronic

OFDR Optical Frequency-Domain Reflectometry

OIF Optical Internetworking Forum

OSA Optical Spectrum Analyzer

### P

PD Photodiode

PDK Process Design Kit

PIC Photonic Integrated Circuit

p-InP p-doped Indium Phosphide

PL Photoluminescence

PLL Phase Locked Loop

PSD Power Spectral Density

### Q

Q-factor Quality Factor QW Quantum Well

### R

R&D Research and Development

RF Radio Frequency

RIN Relative Intensity Noise

S

Si Silicon

SiN Silicon Nitride SiPh Silicon Photonics

SMSR Side Mode Suppression Ratio

SMF Single Mode Fiber

SOA Semiconductor Optical Amplifier

ST Schawlow-Townes

SNR Signal to Noise Ratio

$\mathbf{T}$

TEC Thermoelectric Cooler

TL Tunable Laser TO Thermo-Optic

TRL Technology Readiness Level

U

UGent Ghent University

V

VCSEL Vertical-Cavity Surface-Emitting Laser

W

WDM Wavelength-Division Multiplexing

# Nederlandse samenvatting —Summary in Dutch—

Dit proefschrift presenteert een diepgaand onderzoek naar de ontwikkeling van III-V-op-silicium lasers met smalle lijnbreedte en brede afstembaarheid, evenals halfgeleider optische versterkers (SOA's) met hoge verzadigingsvermogen, gerealiseerd via micro-transferdruk ( $\mu$ TP) integratietechnologie. Het werk speelt in op de groeiende vraag naar schaalbare, hoogpresterende fotonische geïntegreerde schakelingen (PICs) door gebruik te maken van de veelzijdigheid en precisie van μTP om III-V versterkingsmaterialen op siliciumfotonica (SiPh) platformen te integreren. Het bouwt voort op een sterke basis van eerder onderzoek binnen de Photonics Research Group (PRG), waarbij bestaande concepten en architecturen worden uitgebreid tot oplossingen die breed inzetbaar zijn voor verschillende toepassingen en platformen. Het proefschrift begint met het schetsen van de evolutie van optische communicatienetwerken, waarbij de verschuiving van koperverbindingen naar breedbandige, verliesarme optische vezelsystemen wordt benadrukt. Door de exponentiële groei van dataverkeer, aangedreven door cloud computing, videostreaming en AI-workloads, is de behoefte aan compacte, energie-efficiënte en snelle fotonische oplossingen steeds urgenter geworden. Siliciumfotonica, compatibel met CMOS-productieprocessen, biedt een veelbelovend platform voor schaalbare integratie, maar mist intrinsieke lichtbronnen vanwege de indirecte bandstructuur van silicium.

Om deze beperking te overwinnen, onderzoekt het proefschrift verschillende integratietechnieken voor het introduceren van III-V materialen op SiPh platformen, waaronder hybride, heterogene en micro-transferdruk methoden. Van deze technieken blijkt  $\mu$ TP bijzonder krachtig te zijn, doordat het selectieve en schaalbare integratie van vooraf gefabriceerde III-V componenten op silicium mogelijk maakt met submicron-nauwkeurigheid. Het  $\mu$ TP-proces wordt gedetailleerd beschreven, inclusief de principes van kinetisch geschakelde adhesie, het losmaken van componenten door het breken van de verankering, en het gebruik van PDMS-stempels voor overdracht.

De kernbijdrage van dit proefschrift is het ontwerp en de demonstratie van III-V-op-Si lasers met een ultra-brede afstembaarheid en smalle lijnbreedte. Deze lasers zijn geïntegreerd op IMEC 400nm+ platform via  $\mu$ TP van vooraf gefabriceerde SOA's, gebaseerd op eerder werk van de PRG en met een laserarchitectuur die bewust is ontworpen om compatibel en eenvoudig aanpasbaar te zijn voor diverse toepassingen en platformen. De laserarchitectuur omvat Vernier-gefilterde