# Comparison of AWGs and Echelle Gratings for Wavelength Division Multiplexing on Silicon-on-Insulator

Volume 6, Number 5, October 2014

- S. Pathak, Member, IEEE

- P. Dumon, Member, IEEE

- D. Van Thourhout, Senior Member, IEEE

- W. Bogaerts, Senior Member, IEEE

DOI: 10.1109/JPHOT.2014.2361658 1943-0655 © 2014 IEEE

# Comparison of AWGs and Echelle Gratings for Wavelength Division Multiplexing on Silicon-on-Insulator

S. Pathak,<sup>1,2</sup> *Member, IEEE*, P. Dumon,<sup>1</sup> *Member, IEEE*, D. Van Thourhout,<sup>1</sup> *Senior Member, IEEE*, and W. Bogaerts,<sup>1,3</sup> *Senior Member, IEEE*

<sup>1</sup>Department of Information Technology, Ghent University-IMEC, 9000 Ghent, Belgium <sup>2</sup>Department of Electrical and Computer Engineering, University of California Davis, Davis, CA 95616 USA <sup>3</sup>Luceda Photonics, 9200 Dendermonde, Belgium

DOI: 10.1109/JPHOT.2014.2361658

1943-0655 © 2014 IEEE. Translations and content mining are permitted for academic research only. Personal use is also permitted, but republication/redistribution requires IEEE permission. See http://www.ieee.org/publications\_standards/publications/rights/index.html for more information.

Manuscript received August 7, 2014; revised September 26, 2014; accepted September 29, 2014. Date of publication October 7, 2014; date of current version October 15, 2014. Corresponding author: S. Pathak (e-mail: Shibnath.Pathak@intec.Ugent.be).

**Abstract:** We compare the performance (insertion loss and crosstalk) of silicon-based arrayed waveguide gratings (AWGs) and echelle gratings for different channel spacings. For high-resolution de/multiplexer (DWDM) applications, AWGs are the better choice, whereas echelle gratings perform well for low-resolution de/multiplexer (CWDM) applications. Alternatively, for low-resolution de/multiplexer applications, the conventional box-shaped silicon AWG can be modified by an S-shaped AWG. We report crosstalk as low as -27 dB for regular AWGs, whereas in the S-shaped AWGs, the crosstalk is better than -19 dB, with an insertion loss below -2 dB. The crosstalk of the echelle gratings varies between -19 and -23 dB, with insertion loss below -2 dB.

**Index Terms:** AWG.

### 1. Introduction

Arrayed waveguide gratings (AWGs) and echelle gratings (sometimes also called planar concave gratings or PCG) are commonly used for multiplexing and demultiplexing optical signals in wavelength division multiplexing systems (WDM). Both have been demonstrated in various materials systems, including silica-on-silicon [1]–[3], InP [4]–[6], silicon-on-insulator [7]–[10], and germanium-on-silicon [11], [12]. Both devices are based on multi-path interference of light, but the implementation of the delays between the paths is different: in an AWG the different paths are individual waveguides arranged in an array, while in an echelle grating the light travels freely through a slab medium and is reflected by a series of facets. The principle of both devices is explained in Section 2.

AWGs are more commonly used today because they are more fabrication tolerant compared to echelle gratings [13]. The performance of AWGs is mainly dependent on the properties of the dispersive waveguide array, where the performance of echelle gratings depends on the quality of the reflector facets, which are often difficult to define accurately in a planar substrate.

Both types of devices have been realized in high-contrast, submicron silicon-on-insulator (SOI) waveguide platforms [7]–[9], [14]–[17]. On one hand, these SOI devices are attractive

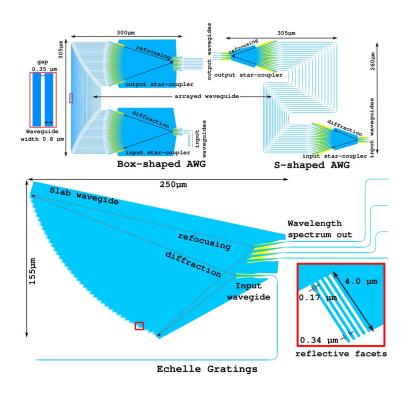

Fig. 1. Schematic diagram of (a)  $8 \times 6.4$  nm box-shape AWG and (b)  $4 \times 24$  nm S-shape AWG.

because of their compact footprint, but on the other hand, the high index contrast makes them very susceptible to phase errors. The origin of these phase errors are different for AWGs and echelle gratings. In an AWG, the main contribution comes from side-wall roughness and width variations in the silicon waveguides, while in the echelle grating, phase errors are mainly caused by errors in the reflectors and global and local wafer thickness variations. Global thickness variations in the slab will introduce defocusing and local thickness variation will introduce path length mismatch. Optimized design schemes and evolving fabrication technology have significantly improved the performance of SOI-based AWGs [7], [8], [15] and echelle gratings [9], [17] to a point where results have been demonstrated that are acceptable for CWDM applications. Still, both types of demultiplexers have their own limitations, and depending on the application and specifications, either one or the other might be preferred. In this paper we draw a comparison between the performance of AWGs and echelle gratings based on their respective merits and limitations, which will help to choose the appropriate device for a given application. To make a classification, we reduce the device specifications to the number of wavelength channels and the channel spacing, and we monitor the performance in insertion loss and channel crosstalk. We then experimentally demonstrate and characterize the silicon AWGs and echelle gratings for different channel spacings in the same technology platform. To identify these demultiplexers we follow a common naming methodology, e.g., number-of-output-channels × channel-spacing type-of-demux. For example, 4 × 10 nm indicates a device with four wavelength channels with a 10 nm spacing.

# 2. Operating Principle

### 2.1 Arrayed Waveguide Gratings

An AWG consists of an input star coupler, an array of waveguides, and an output star coupler. When operating as a demultiplexer, light coming from the input waveguide enters the input star-coupler and is distributed over the arrayed waveguides through in-plane diffraction. After propagating through the waveguide array contributions coming from all waveguides interfere in the output star coupler. Two examples of SOI-based AWG designs are shown in Fig. 1. The optical path length difference between two successive waveguides of the waveguide array is constant, and chosen such that for the center wavelength all contributions are in phase. As a result, the input image will be reproduced at the center output channel. As the AWG uses two separate slab regions for diffraction and refocusing the design and positioning of the input and output waveguide apertures can be largely decoupled.

The phase difference in the array waveguides changes with wavelength, which will introduce a lateral shift of the field in the image plane, and the light will be coupled into another output waveguide. When the phase relationships in the arms are perfectly conserved, the imaging can

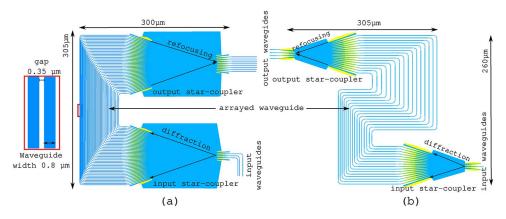

Fig. 2. Variation of the delay length and minimum gap between the waveguides with FSR for box-shaped AWGs.

be very good and will improve with an increasing number of arms. However, in imperfect waveguides (e.g., with local width variation due to sidewall roughness and local thickness deviations) there will be minute deviations from the designed optical path length, which will translate into phase errors. Phase errors will cause aberrations in the imaging, resulting in light coupled to the wrong output: channel crosstalk. If the cause of the phase errors is stochastic, the average phase error in each arm will be proportional to  $\sqrt{L}$ , with L the length of the arm [18].

The length difference between the waveguide arms (delay length) relates directly to the *Free Spectral Range* (FSR) of the AWG: the wavelength span between different diffraction orders of the grating. As shown in Fig. 2 larger delays translate in a smaller FSR and larger gap between the waveguides for box-shape AWGs. When the FSR is 65 nm the delay length become so small that the minimum gap between the waveguides become nearly zero. Therefore, it is difficult to create a horseshoe or rectangular design to obtain larger FSR (above 65 nm) without overlapping the waveguides. As the requirement of FSR for CWDM applications is 100 nm or higher a modified design, such as the S-shaped layout shown in Fig. 1(b) may be needed. Such design requires longer waveguides however, which might impact overall performance.

For a given FSR, the channel spacing in an AWG determines the number of waveguides required in the array. As a rule of thumb, the number of arms is set to be three to four times the number of channels within an FSR:

$$N_{arms} pprox 3.5 rac{FSR}{\Delta \lambda_{channel}}$$

(1)

Many channels therefore means many arms in the array, and a larger device. On average, the arms will also be longer, and therefore more phase errors will accumulate by the time the light reaches the output star coupler. We can expect that for a given technology, AWGs with a higher number of channels will exhibit a higher crosstalk level than devices with fewer channels.

## 2.2 Echelle Gratings

The operating principle of an echelle grating is similar to that of an AWG in the sense that multi-path interference with a set of equally spaced delay lengths is used. However, the delays are now implemented in the free propagation region itself, using reflective facets. This means that the same slab area is used for diffraction and refocusing. While this is a more efficient use of space it puts restrictions on the position of the input and output waveguides.

As with the AWG, the optical group delay length difference between facets determines the FSR. In silicon, the slab waveguide has significantly lower dispersion and thus a lower group index compared to the waveguides used in an AWG. This means that the physical delay length needs to be larger than in an AWG to obtain the same FSR. This causes an echelle grating to grow faster in footprint than a comparable AWG when many facets are needed. However, for a

large FSR and few channels, echelle gratings can be extremely compact. Moreover, they do not suffer from layout restrictions for very short delays, making them very suitable as CWDM demultiplexers with few, widely spaced channels.

As with an AWG, crosstalk in an echelle grating can be attributed to imperfect imaging of the refocused light. The errors in the image can be attributed to two causes: phase errors in the different paths traveled by the light, and imperfect reflection and scattering by the facets. The phase errors in an echelle gratings accumulate in the slab region, and the variations in optical path length can be largely attributed to local thickness variations. As the thickness changes typically occur on longer length scales and are not as stochastic in nature as line-width variations in waveguides, the phase errors do not necessarily follow the same  $\sqrt{L}$  rule as with AWGs. Instead larger echelle gratings will suffer disproportionately from crosstalk compared to AWGs.

As for the role of the grating facets, this is an inherent problem of the design of echelle gratings, combined with technology limitations: the grating facets will always suffer from corner effects, which will cause undirected scattering. The smaller the facets, the larger the effect of these corners. Using larger facets alleviates this issue but will increase the size of the device.

### 3. Design

We designed, simulated, fabricated and measured a set of AWGs and echelle gratings with different values of FSR and channel spacing, and compared both the design metrics (e.g., footprint) and the performance metrics (insertion loss, crosstalk). The design and simulation were done with IPKISS [19]–[21].

All devices were designed for IMEC's passive SOI platform; the substrate is an SOI wafer with 220 nm thick silicon on top of a 2  $\mu$ m buried oxide layer. The designs are patterned using 193 nm deep UV lithography, and take into account the minimum feature sizes allowed by this process. We also make best use of the double etch process of the platform [8]: A full, 220 nm deep etch is used to define the high contrast waveguides (further referred to as the deep etch) and bends, while a 70 nm etch defines the low contrast apertures in the star coupler regions (further referred to as shallow etch).

### 3.1. Arrayed Waveguide Grating

The design procedure for the AWGs is documented in earlier publications [7], [14], [15]. The waveguide array consists of 450 nm wide (single mode) waveguides in the bent sections and 800 nm wide (multi mode) waveguides in the straight sections, to reduce the accumulation of phase errors. The lengths of the 450 nm sections is kept the same for all arms, and the entire delay is in the wider waveguide sections. As discussed, the main problem impacting the performance of silicon AWGs are phase errors, which increase when using longer delay lines. As we increase the FSR (or the channel spacing for a fixed number of channels per FSR), the delay length will decrease, which reduces the phase error. At the same time in the layout, the pitch between adjacent waveguides will also decrease, which can increase evanescent coupling between two waveguides, and can thereby also result in extra phase errors.

When the FSR (or channel spacing) increases further, the waveguides in the rectangular array will come too close. For example, for the 8  $\times$  6.4 nm box-shape AWG shown in Fig. 1(a), which has FSR of 64 nm, the minimum gap between two waveguides in the array is only 0.35  $\mu$ m, which will lead to excessive coupling. In such cases an alternative layout is needed. Using S-shaped waveguides it is possible to design a AWG with very low channel spacing, even down to a zeroth-order AWG whereby the two star-couplers are connected with equal length waveguides, while keeping the waveguides in the array uncoupled. But even the shortest waveguide of an S-shaped AWG will be longer than it would be in a box-like design, and will contain two additional bends. This will introduce additional phase errors, and increase the insertion loss and the crosstalk. Fig. 1(b) shows a schematic diagram of a 4  $\times$  24 nm S-shaped AWG. The footprint of S-shaped AWGs is obviously also larger than that of box-shaped AWGs:

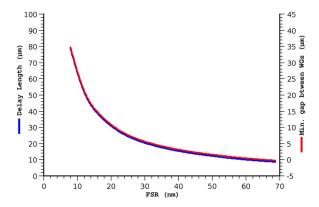

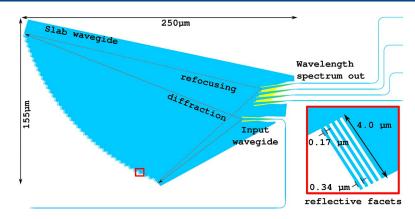

Fig. 3. Schematic diagram of 4  $\times$  20 nm echelle grating.

The size of the 4  $\times$  6.4 nm box-shaped AWG is 275  $\times$  245  $\mu$ m<sup>2</sup> while the size of the 4  $\times$  24 nm S-shaped AWG is 305  $\times$  260  $\mu$ m<sup>2</sup>.

### 3.2 Echelle Grating

The design of the echelle gratings is based on a Rowland geometry and the design procedure was detailed in [10]. As for the AWGs the input and output apertures are shallowly etched to reduce reflections. As shown in Fig. 3, the reflectors consist of first-order distributed Bragg reflectors (DBR) with four deeply etched trenches of 170 nm width and 340 nm pitch. For all the echelle grating designs the angle of incidence and diffraction are 41 and 34 degrees, respectively. Fig. 3 shows the schematic diagram of a 4  $\times$  20 nm echelle grating: the footprint is 250  $\times$  155  $\mu \text{m}^2$ . The device size increases rapidly as we decease the channel spacing/FSR: The size of the 4  $\times$  6.4 nm echelle grating is 275  $\times$  245  $\mu \text{m}^2$ .

### 4. Results and Discussions

To characterize the devices we used 1-D curved grating couplers to couple the light in and out of the chip. The grating couplers are designed to couple only a single polarization (TE). The compact curved grating couplers have a limited 3 dB bandwidth of about 60 nm. Also, the optimal alignment is wavelength dependent. This has to be taken into account when measuring demultiplexer devices: When aligning each output at the peak wavelength of the channel, the transmission of the on-chip device will be overestimated after normalization with the transmission through a reference waveguide. We compensate for this by collecting normalization data for all wavelengths.

### 4.1 Arrayed Waveguide Gratings

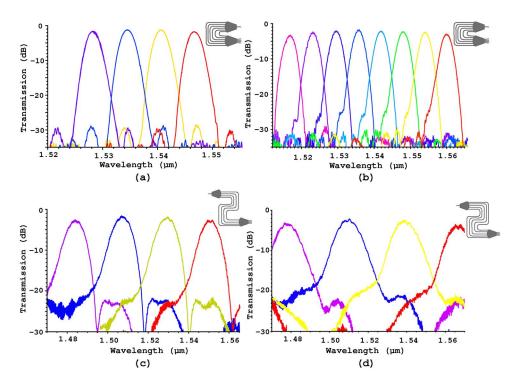

The 4  $\times$  6.4 nm box-shape AWG has a measured insertion loss of -1.53 dB and a -27.1 dB crosstalk level. If we keep the channel spacing constant, but increase the number of channels, the FSR increases and hence the delay length goes down. However the number of waveguides required in the array increases (see (1)). Overall, this does not significantly increase the device footprint. As the average delay line length does not change significantly either, the impact on the crosstalk is negligible. For example, for the 8  $\times$  6.4 nm box-shape AWG the insertion loss and the crosstalk are -1.86 dB and -27.3 dB respectively. Table 1 shows the performance of all the AWGs. As we can see from Table 1 there is a mismatch between the average channel spacing and the design values, which can be explained by the global waveguide width and wafer thickness variation.

If we keep the number of channels constant (4) but increase the channel spacing (and thus the FSR as well), we need to change the shape of the AWG to an S-shape. The much longer

TABLE 1

Comparison of Size, Delay L (center waveguide/slab length), Spacings (design  $\rightarrow$  measured average channel spacing), WG/GF (number of waveguides/grating facets), Loss (insertion loss  $\rightarrow$  non-uniformity), and XT (crosstalk level) between AWGs and echelle gratings

| Device          | Area      | Delay L | Ch | Spacings | WG / | Loss       | XT    | FSR  |

|-----------------|-----------|---------|----|----------|------|------------|-------|------|

| Type            | $\mu m^2$ | $\mu$ m |    | (nm)     | GF   | (dB)       | (dB)  | (nm) |

| Box-shaped AWG  | 275×245   | 300     | 4  | 6.4→6.27 | 24   | -1.53→0.37 | -27.1 | 38   |

| Box-shaped AWG  | 310×305   | 290     | 8  | 6.4→6.17 | 40   | -1.86→1.16 | -27.3 | 64   |

| S-shaped AWG    | 305×260   | 395     | 4  | 24→22.3  | 16   | -1.68→1.10 | -20.6 | 88   |

| S-shaped AWG    | 305×260   | 386     | 4  | 32→30    | 16   | -2.1→1.75  | -19.1 | 144  |

| Echelle Grating | 700×420   | 1055    | 4  | 6.4→6.22 | 70   | -1.43→0.24 | -18.7 | 70   |

| Echelle Grating | 700×385   | 1060    | 8  | 6.4→6.17 | 90   | -1.55→1.1  | -19.7 | 100  |

| Echelle Grating | 450×220   | 655     | 4  | 10→9.62  | 60   | -1.57→0.89 | -24.2 | 120  |

| Echelle Grating | 250×155   | 345     | 4  | 20→20.2  | 40   | -2.2 →0.55 | -23.3 | 120  |

Fig. 4. Experimental result of AWGs. (a) 4  $\times$  6.4 nm, (b) 8  $\times$  6.4 nm, (c) 4  $\times$  24 nm, and (d) 4  $\times$  32 nm.

delay lines in this device induce a penalty: For a 4  $\times$  24 nm S-shape AWG, we measured an insertion loss of -1.7 dB and crosstalk of -20.6 dB. The performance of a 4  $\times$  32 nm S-shaped AWG is even worse: the measured insertion loss is -2.0 dB and the crosstalk is -19.1 dB. Fig. 4 shows the measured transmission spectrum of the AWGs discussed above.

### 4.2 Echelle Grating

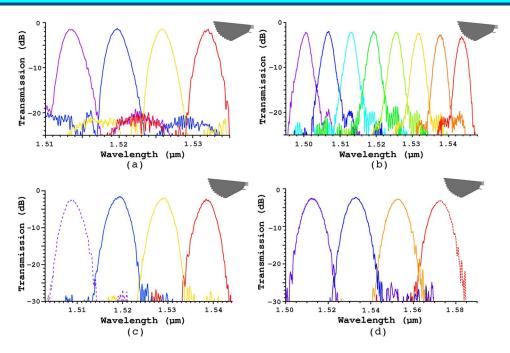

The 4  $\times$  6.4 nm echelle grating has a measured insertion loss of -1.43 dB and a crosstalk of -18.7 dB. This is significantly worse than the AWG with the same specifications. The channel spacing is quite small for an echelle grating, and it needs a very large slab region, which induces large phase errors. The performance improves when we increase the channel spacing (and thus the FSR): the crosstalk of the 4  $\times$  10 nm echelle grating drops to -24.2 dB, and the

Fig. 5. Experimental result of echelle grating. (a) 4  $\times$  6.4 nm, (b) 8  $\times$  6.4 nm, (c) 4  $\times$  10 nm, and (d) 4  $\times$  20 nm.

insertion loss is -1.6 dB. Further incrementing the channel spacing makes the echelle grating more sensitive to the size of the grating teeth and their positioning. For the 4  $\times$  20 nm echelle grating the crosstalk is -23.3 dB and the insertion loss increases to -2.2 dB. The transmission spectra of these echelle gratings are shown in Fig. 5. The dotted lines in Fig. 5 indicate an accidentally damaged output channel or a spectrum outside the range of the tunable laser used for characterization. Table 1 shows the performance of all the echelle gratings. Just as with the AWG the average channel spacings does not entirely match the design because of wafer thickness variation.

For both AWGs and echelle gratings the insertion loss of the side channels is higher, and can be as large as -3 dB when channels are at the edge of the FSR. This is inherent to the imaging mechanisms used. To reduce the non-uniformity due to this roll-off, it is often better to make the FSR larger than the product of the number of channels and the channel spacing [7]. This can also be deduced from Table 1 for both AWGs and echelle gratings.

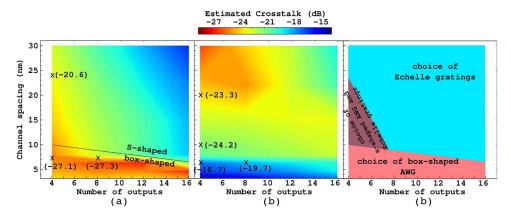

Based on these experimental results and further simulation, we estimated the crosstalk level of AWGs and echelle gratings as function of their channel spacing and number of wavelength channels within a full FSR. Fig. 6(a) and (b) shows the simulated crosstalk for both types of devices. Fig. 6(c) shows the expected best working regions for each type of device. As shown in Fig. 6(a) for a constant channel spacing the crosstalk of an AWG will improve with increasing number of wavelength channels, assuming that the phase errors originate from the waveguide array only. For S-shaped AWGs the crosstalk increases due to the increasing length of the smallest delay line. The black line indicates the border between the box and S-shape AWG. For echelle gratings, as the FSR increases (either by increasing the number of wavelength channels or by increasing the channel spacing) the crosstalk decreases. From Fig 6(c) it is clear that for a high-resolution de/multiplexer, the box-shape AWG layout is to be preferred. For low resolution de/multiplexing an echelle grating is the best choice. S-shaped AWGs are an alternative for low resolution de/multiplexing with smaller number of wavelength channels. An added benefit of the AWG is that it is easier to actively tune or trim the waveguides individually [22]. In such tuning or trimming is applied, it will have an advantage over the echelle grating for all combinations of channel spacing and number of channels.

Fig. 6. The estimated crosstalk mapping of (a) AWG and (b) echelle grating. (c) Estimated design of best performance de/multiplexers. (Black cross) The measured crosstalk of the devices reported in Table 1.

### 5. Conclusion

We compare the performance of two grating based wavelength de/multiplexers in silicon: arrayed waveguide gratings and echelle gratings. The echelle gratings are the best choice for low resolution (CWDM) de/multiplexer applications. For high resolution de/multiplexer applications AWGs are a better choice. For larger channel spacings AWGs suffer from layout restrictions, which can be overcome by using an S-shaped geometry, but at the cost of performance. We presented AWG and echelle gratings with insertion losses below 2 dB, and crosstalk down to -27 dB. We also showed S-shaped AWGs with decent performance for CWDM applications. with insertion loss and the crosstalk of -1.7 dB and -20.6 dB. It is obvious that any improvement in fabrication will help to improve the performance: reduced sidewall roughness will reduced the phase error in the arrayed waveguide and it will also improve the reflection of the grating facets used in echelle gratings, improved wafer thickness variation will improve the performance of the slab waveguide, etc. When such technology improvements or even new techniques (e.g., active tuning, new concepts for facet reflectors etc.) are introduced, this type of study needs to be performed again to assess the relative merits of the different device types. We can expect the overall trends to be similar as presented here, but the position of the separation lines in Fig. 6 could change, favoring either AWGs or echelle gratings.

### References

- [1] R. Adar, C. Henry, C. Dragone, R. Kistler, and M. Milbrodt, "Broad-band array multiplexers made with silica wave-guides on silicon," *J. Lightw. Technol.*, vol. 11, no. 2, pp. 212–219, Feb. 1993.

- [2] Y. Inoue, A. Himeno, K. Moriwaki, and M. Kawachi, "Silica-based arrayed-waveguide grating circuit as optical splitter/router," Electron. Lett., vol. 31, no. 9, pp. 726–727, Apr. 1995.

- [3] S. Janz et al., "Planar waveguide echelle gratings in silica-on-silicon," IEEE Photon. Technol. Lett., vol. 16, no. 2, pp. 503–505, Feb. 2004.

- [4] H. Bissessur *et al.*, "16 channel phased array wavelength demultiplexer on InP with low polarization sensitivity," *Electron. Lett.*, vol. 30, no. 4, pp. 336–337, Feb. 1994.

- [5] M. Zirngibl, C. Dragone, and C. Joyner, "Demonstration of a 15 × 15 arrayed waveguide multiplexer on InP," *IEEE Photon. Technol. Lett.*, vol. 4, no. 11, pp. 1250–1253, Nov. 1992.

- [6] J. He et al., "Monolithic integrated wavelength demultiplexer based on a waveguide rowland circle grating in InGaAsP/InP," J. Lightw. Technol., vol. 16, no. 4, pp. 631–638, Apr. 1998.

- [7] S. Pathak, M. Vanslembrouck, P. Dumon, D. Van Thourhout, and W. Bogaerts, "Optimized silicon AWG with flattened spectral response using an MMI aperture," *J. Lightw. Technol.*, vol. 31, no. 1, pp. 87–93, Jan. 2013.

- [8] W. Bogaerts et al., "Silicon-on-insulator spectral filters fabricated with CMOS technology," IEEE J. Sel. Topics Quantum Electron., vol. 16, no. 1, pp. 33–44, Jan./Feb. 2010.

- [9] J. Brouckaert et al., "Planar concave grating demultiplexer with high reflective Bragg reflector facets," IEEE Photon. Technol. Lett., vol. 20, no. 4, pp. 309–311, Feb. 2008.

- [10] J. Brouckaert, W. Bogaerts, P. Dumon, D. Van Thourhout, and R. Baets, "Planar concave grating demultiplexer fabricated on a nanophotonic silicon-on-insulator platform," *J. Lightw. Technol.*, vol. 25, no. 5, pp. 1269–1275, May 2007.

- [11] A. Malik *et al.*, "Germanium-on-silicon mid-infrared arrayed waveguide grating multiplexers," *IEEE Photon. Technol. Lett.*, vol. 25, no. 18, pp. 1805–1808, Sep. 2013.

- [12] A. Malik, M. Muneeb, Y. Shimura, J. Van Campenhout, and G. Roelkens, "Germanium-on-silicon mid-infrared wave-guides and Mach-Zehnder interferometers," in *Proc. IEEE Photon. Conf.*, 2013, pp. 104–105.

- [13] K. Okamoto, "Wavelength-division-multiplexing devices in thin SOI: Advances and prospects," *IEEE J. Sel. Topics Quantum Electron.*, vol. 20, no. 4, pp. 1–10, Jul. 2014.

- [14] S. Pathak, D. Van Thourhout, and W. Bogaerts, "Design trade-offs for silicon-on-insulator-based AWGs for (de)multiplexer applications," *Opt. Lett.*, vol. 38, no. 16, pp. 2961–2964, Aug. 2013.

- [15] S. Pathak *et al.*, "Effect of mask discretization on performance of silicon arrayed waveguide gratings," *IEEE Photon. Technol. Lett.*, vol. 26, no. 7, pp. 718–721, Apr. 2014.

- [16] J. Wang et al., "Low-loss and low-crosstalk 8 × 8 silicon nanowire AWG routers fabricated with CMOS technology," *Opt. Exp.*, vol. 22, no. 8, pp. 9395–9403, Apr. 2014.

- [17] F. Horst, W. M. J. Green, B. Offrein, and Y. Vlasov, "Silicon-on-insulator echelle grating WDM demultiplexers with two stigmatic points," *IEEE Photon. Technol. Lett.*, vol. 21, no. 23, pp. 1743–1745, Dec. 2009.

- [18] T. Goh, S. Suzuki, and A. Sugita, "Estimation of waveguide phase error in silica-based waveguides," *J. Lightw. Technol.*, vol. 15, no. 11, pp. 2107–2113, Nov. 1997.

- [19] IPKISS. [Online]. Available: http://www.ipkiss.be

- [20] Luceda Photonics. [Online]. Available: www.lucedaphotonics.com

- [21] M. Fiers *et al.*, "Improving the design cycle for nanophotonic components," *J. Comput. Sci.*, vol. 4, no. 5, pp. 313–324, Sep. 2013.

- [22] F. Soares *et al.*, "Monolithic InP 100-channel × 10-GHz device for optical arbitrary waveform generation," *IEEE Photon. J.*, vol. 3, no. 6, pp. 975–985, Dec. 2011.