## SILICON PHOTONICS

R. Baets, P. Dumon, W. Bogaerts, G. Roelkens, J. Van Campenhout,

D. Taillaert, J. Brouckaert, K. De Vos, J. Roels, S.K. Selvaraja, F. Van Laere, P. Bienstman, D. Van Thourhout

Ghent University-IMEC

Department of Information Technology,

St. Pietersnieuwstraat 41, B-9000 Gent, Belgium

roel.baets@intec.ugent.be

#### **A**BSTRACT

Silicon photonics is rapidly gaining importance as a generic technology platform for a wide range of applications in telecom, datacom, interconnect and sensing. It allows to implement photonic functions in or above silicon through the use of wafer-scale technologies normally used for advanced CMOS-processing. In recent years there has been a plethora of breakthroughs in this field, including the demonstration of ultra-compact passive optical functions, high speed optical modulators and detectors, silicon lasers, all-optical signal processing functions, etc. One of the exciting new directions is the wafer-scale heterogeneous integration of III-V materials with silicon.

#### INTRODUCTION

The integration of micro-photonic functions in Silicon or above Silicon has for many years been considered to be a holy grail, since it was expected to enable complex low-cost photonic integrated circuits in a way similar to what has happened in the field of microelectronics. There are already several established examples - both in high volume markets as well as in specialized niche markets - where this dream has come true. These include for example Silicon camera chips, MEMS- or liquid crystal based microdisplays above Silicon, Silica-on-Silicon planar lightwave circuits for functions in WDM telecom networks etc.

In recent years a new technology has been emerging from research labs worldwide: the use of standard Silicon-on-Insulator (SOI) wafers and standard CMOS processing technologies to create ultra-compact so-called "nano-photonic" components and circuits in Silicon [1-3]. In these circuits one uses high refractive-index-contrast single-mode waveguides with a cross-section of the order of the wavelength squared to make passive or active devices. The core of the waveguide is Silicon while the cladding is either a dielectric such as silica or air. The waveguide can be a conventional waveguide based on guiding by total internal reflection or a photonic crystal waveguide based on guiding by Bragg diffraction. The active functions — light emission, modulation, switching, amplification, detection - can be based on the properties of Silicon itself or on the properties of a special cladding material.

The term "nano-photonic" calls for some interpretation. The typical smallest feature sizes – widths, thicknesses, lengths – in wavelength-scale photonic structures are in the range of one tenth of a wavelength to one wavelength. For operation at a wavelength of 1550 nm for example – corresponding to a wavelength in Silicon of about 500 nm – the required smallest feature sizes are typically between 50 and 500 nm. This matches nicely the capabilities of present day's CMOS technology. However, the accuracy and reproducibility of the spectral behaviour of the optical functions are directly correlated to the geometric accuracy of these features in the device. As a rule of thumb one can say that a spectral accuracy of 1 nm (relative to a wavelength of 1550 nm) translates into a geometric accuracy of 1 nm (relative to a feature size of 50-500 nm).

Furthermore the high-index contrast interfaces in these devices need to be smooth down to the 1 nm level to avoid scattering losses.

### RATIONALE FOR SOI NANOPHOTONICS

There are many arguments in favour of Silicon-on-Insulator nanophotonics: functionality and performance arguments, technological arguments and economical arguments.

In terms of functionality and performance the SOI platform distinguishes itself from most planar waveguide platforms in terms of the high vertical index contrast. Combined with etching through the (thin) Silicon core the resulting waveguides have a high index contrast both vertically and horizontally. With this contrast the waveguide cross-section becomes very small and the interwaveguide spacing can be very small before coupling effects occur. Furthermore one can make virtually lossless curved waveguides with very small radii of curvature - down to a few micrometer - and this has a large impact on circuit layout. In terms of functional components the high index contrast has enormous merits for microcavities, which undoubtedly can be considered to be one of the most important generic components for passive and active functions. High index contrast is the key to achieve microcavities with small cavity volume and high cavity quality factor [4-5]. The high confinement and field enhancement brought by high index contrast and by cavity effects can also be exploited in non-linear optical components so as to turn weak non-linear effects into practical performance at low power levels.

Since Silicon is not a suitable material for all types of active functionality one has to make use of heterogeneous integration in which overlay materials are combined with SOI waveguides. By modifying the Silicon waveguide dimensions one can tailor the overlap of the optical field with the overlay material. In principle one could use several functional overlay materials on the same chip.

A last functionality argument in favour of SOI is of course the fact that one can integrate nano-photonic functions with microelectronic circuitry.

The technological arguments in support of SOI technology are heavyweight arguments. Silicon technology has reached a level of maturity which outperforms any other planar chip manufacturing technology by orders of magnitude in terms of performance, throughput and reproducibility. The processes, once developed, are amazingly reproducible across a wafer and from wafer to wafer. The processes needed to define the basic waveguide structure in SOI nano-photonic circuits are fully compatible with front-end processes for fabricating CMOS.

Finally there are strong economic arguments supporting SOI nano-photonics. First of all, large diameter SOI wafers of very good quality are commercially available at moderate cost, at least if one uses a standard type of wafer. When one processes nano-photonic ICs by means of wafer scale processes on these large wafers, the

resulting cost per chip will be small. Furthermore several groups have demonstrated techniques for wafer-level testing of photonic-components by using surface coupling techniques from vertical optical fibers into horizontal on-wafer waveguides. This wafer-level testing can in principle be highly automated. Since the cost of a photonic module is very often dominated by packaging it is important to make this packaging as simple as possible. In recent years several techniques have been successfully demonstrated in which a spot-size converter is integrated on the chip by means of wafer-scale techniques, thereby making the packaging simpler and cheaper.

The main economic driver for SOI-based nano-photonics may well be the fact however that one can operate a photonic IC company in a fabless way, whereby the key front-end technological processes are subcontracted to a foundry-like Silicon CMOS fab. This is of key importance as long as the product volumes do not allow for the ownership of a dedicated fab. This is the case for the majority of photonic IC applications today.

#### THE SILICON PHOTONICS FOOD CHAIN

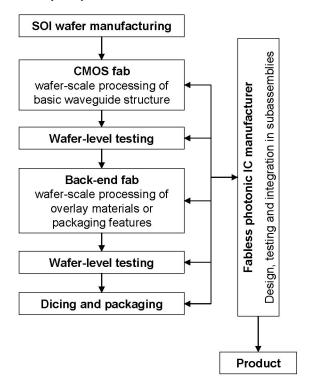

Figure 1 shows a possible future process flow for the manufacturing of an SOI nano-photonic component. Each block in the diagram could in principle represent a different industrial actor.

The product developer is assumed to be a fabless company that takes care of the entire product specification, design, the testing of packaged components and their integration in subassemblies or even in complete systems.

Figure 1. Possible process flow for the manufacturing of SOI nano-photonic components.

The SOI wafer manufacturer delivers 200 or 300 mm SOI wafers to the CMOS fab. He will offer a small number of standard SOI-wafers for photonic applications with different thicknesses for the Silicon and the silica layer and possibly even variants with multiple Silicon layers.

The CMOS fab will use its standard CMOS processes for the fabrication of the nano-photonic IC's. Depending on the smallest feature size it will choose the most appropriate lithography process. For many types of components a 248 nm deep UV process will suffice, but for demanding applications the choice will be to use a 193 nm stepper. In special cases one may need to use immersion lithography or extreme UV lithography. Whatever standard processes available for CMOS can be used for nano-photonic circuits.

An important cost factor, especially in low volume applications and in prototyping, is the mask cost. If this turns out to be an issue it may make sense to collect many designs on a single mask, thereby sharing the cost between different products or different companies.

The etching processes needed to define the waveguides are in principle within reach of CMOS etching processes but the required geometrical accuracy and interface smoothness may require that these processes are optimized to a "photonic grade" level. In recent years it has been demonstrated that SOI photonic wires defined by deep UV optical lithography and CMOS etching processes can produce low loss waveguides [1].

After processing of the basic waveguide structures the wafers will be automatically tested. This is particularly important for functions with a strong wavelength selectivity. The geometrical accuracy requirements are very extreme in this case and may be at the limit of the CMOS fab capability. Automated wafer-level testing will allow to select good dies or to identify the parameters for a later automated trimming process. The wafer-level testing is only possible of course when the circuits are provided with surface coupling structures allowing to couple light from a fiber or from a microscope objective into the chip. Such coupling structures can easily be realized and good coupling efficiencies – beyond 50% - have been demonstrated [6]

The wafers then move to back-end processing. This step will be much less generic than the previous steps and will be very much product specific. It may involve overlay materials (and their structuring) for active functionality or for simple packaging or for trimming. Some overlay functions are relatively straightforward and have already been demonstrated today at research level. Examples include adiabatic transitions to fiber matched spin-on polymer waveguides for easy fiber coupling [7] and liquid crystal overlays for tuning. Other overlay functions are beyond today's state of the art: an example is the integration of an electrically fed bonded membrane InP microlaser or optical amplifier coupling efficiently into an SOI waveguide [8-9]. In any case it is important that the back-end processes are as much as possible wafer-scale processes.

The back-end processing may be followed by another wafer-level testing step, after which the wafers move to a packaging company where they are diced and mounted in a package with optical and possibly also electrical and thermal interfaces. The packaged components are then tested and possibly integrated into a (sub)system.

In the case where SOI nano-photonic functions need to be integrated with CMOS logic, the overall process flow of fig. 1 does not change much conceptually, except that the wafers will undergo a complex set of processes in the CMOS fab. Any process in the

backend stages will then need to be compatible (in terms of chemicals and thermal budget) with the presence of the electronic circuitry.

At the research level there is a need to develop multi-project-wafer services for silicon photonics. An early example of such a service is operational in the European Silicon Photonics platform, an initiative developed under the Network of Excellence ePIXnet [11-12].

#### **A**PPLICATIONS

The process flow described in the previous section only makes sense if there are applications of sufficient volume. It is impossible to imagine and predict all the applications of SOI nanophotonic ICs but some examples of such applications are given hereafter.

- Transceivers for high data rate telecom and datacom (high speed ethernet, fiber-to-the-home...): integration of a high speed optical transmitter (light source, modulator, drive electronics) with a high speed receiver (detector, receiver electronics), a duplexer and possibly coarse WDM functionality.

- Dense WDM components for telecom applications: arrayed waveguide gratings [10], possibly integrated with detectors and receiver electronics; add-drop multiplexers, possibly reconfigurable; tunable lasers etc.

- Sensors: strain sensors, spectroscopic sensors, bio-sensors [13], labs-on-a-chip etc.

- Optical interconnect: provide a solution for the interconnect bottleneck in high-end CMOS circuits by building a photonic interconnect layer above CMOS, involving microlasers, dense waveguides and microdetectors [14]

- Digital photonics: integrate optical logic gates and optical memory elements for digital all-optical processing at ultra-high data rate.

#### **C**ONCLUSIONS

We have reviewed the rationale behind the rapid emergence of Silicon-on-Insulator nano-photonics. A model has been presented for an industrial process flow in which fabless photonic IC manufacturers develop novel products based on CMOS foundry access, wafer-scale back-end processing and automated wafer-scale testing. The wide range of potential applications of this generic technology are discussed.

#### ACKNOWLEDGEMENTS

This work was supported by the EU through the the IST-ePIXnet Network of Excellence and the IST-PICMOS project as well as by the Belgian IAP Network *photonics@be*.

# REFERENCES

- [1] W. Bogaerts et al., IEEE J. Lightwave Techn., 23(1), p.401-412

- [2] Y. A. Vlasov et al., Optics Express Vol. 12 (8), pp. 1622-1631

- [3] M. Notomi et al, Opt. Express, vol. 12 (8), pp. 1551–1561 (2004)

- [4] M. Borselli et al, Opt. Express, Vol. 13, (5), pp. 1515-1530, (2005)

- [5] W. Bogaerts et al, J. Selected Topics in Quantum Electronics, 12(6), p.1394-1401 (2006)

- [6] D. Taillaert et al, Japanese Journal of Applied Physics, 45(8A), p.6071-6077 (2006)

- [7] T. Shoji et al., 15th annual meeting of the IEEE Lasers and Electro-Optics Society, vol. 1, p.289-290, (2002)

- [8] G. Roelkens et al, Optics Express, 14(18), p.8154-8159 (2006)

- [9] R. Romeo et al, Optics Express, 14(9), p.3864-3871 (2006)

- [10] P. Dumon et al, Group IV Photonics, Hong Kong, p.WB5 (2004)

- [11] R. Baets et al, 32nd European Conference on Optical Communication (ECOC 2006), France, p.125-126 (2006)

- [12] www.epixnet.org and www.siliconphotonics.eu

- [13] K. De Vos et al, SPIE Photonics West Symposium on Biomedical Optics (BiOS), San Jose, (2007)

- [14] D. Van Thourhout et al, 18th Annual Meeting of the IEEE Lasers & Electro-Optics Society (LEOS 2005), Australia (2005)