# A nanophotonic InP/InGaAlAs optical amplifier integrated on a SOI waveguide circuit

M. Tassaert\*, S. Keyvaninia\*, D. Van Thourhout\*, W.M.J. Green<sup>†</sup>, Y. Vlasov<sup>†</sup> and G. Roelkens\*

\*Photonics Research Group - Ghent University/imec, Sint-Pietersnieuwstraat 41, B-9000 Gent, Belgium

†IBM T.J. Watson Research Center, 1101 Kitchawan Road, Yorktown Heights, NY 10598, USA

Abstract—We demonstrate over 8 dB gain in pulsed regime in an InP/InGaAlAs membrane waveguide heterogeneously integrated on a Silicon-On-Insulator waveguide circuit and optically pumped through the silicon waveguide layer, using a peak pump power of only 4.5 mW. This is an important step towards a CMOS-compatible optical amplifier for intra-chip optical interconnects.

#### I. INTRODUCTION

Silicon-On-Insulator (SOI) is an excellent platform for the realization of passive optical functions. The high index contrast waveguides that can be achieved show low loss and allow for very tight bends, reducing the footprint of photonic integrated circuits. Furthermore, the fabrication of SOI photonic integrated circuits is CMOS compatible, so it allows for integration of both electronics and photonics on a single die. However, most applications also require active optical functions, such as lasers and detectors. Due to silicon's indirect band gap, creating active devices on SOI remains a challenge. One approach to circumvent this problem is by heterogeneous integration of a III-V layer stack on the SOI waveguide circuit. This can be done by adhesive die-to-wafer bonding, using DVS-BCB as a bonding agent [1]. Several types of lasers have already been demonstrated using this technique [2]. In these approaches however, one typically uses a thick III-V waveguide with a thickness of more than 500 nm. Although this allows for efficient current injection, the confinement of the mode in the active layers is limited. By reducing this thickness, high index contrast III-V membrane waveguides can be created which reach a much higher confinement in the active layers. In this paper we propose to use a 100 nm thick III-V membrane waveguide that is optically pumped from the underlying SOI waveguide layer to create on-chip optical amplifiers.

# II. DEVICE LAYOUT

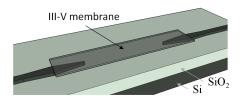

The device structure is schematically shown in figure 1. It consists of a III-V membrane coupled adiabatically to the underlying SOI waveguide layer by  $10\,\mu\mathrm{m}$  long inverted taper couplers. These couplers consist of a linearly tapered  $220\,\mathrm{nm}$  thick silicon wire from a width of  $700\,\mathrm{nm}$  near the III-V strip waveguide edge to a width of less than  $100\,\mathrm{nm}$  to achieve a nearly adiabatic transition from the SOI to the III-V strip

Martijn Tassaert acknowledges the Bijzonder Onderzoeksfonds (BOF) for a doctoral grand.

Fig. 1. Schematic view of the III-V strip waveguide coupled to the SOI circuit by two inverted tapers.

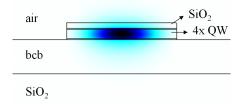

Fig. 2. Mode profile in the III-V strip waveguide

waveguide. Both the signal and pump light are injected in the III-V membrane through the SOI waveguide layer. Light is coupled in the SOI waveguides using a vertical grating coupler with an insertion loss of  $5.5\,\mathrm{dB}$ . The III-V strip waveguide has a width of  $2\,\mu\mathrm{m}$  and consists of four compressively strained  $(0.85\,\%)$  AlGaInAs quantum wells of 7 nm with five tensile strained AlGaInAs  $(0.55\,\%)$ , Q1.3) barriers of 10 nm and two 10 nm InP cladding layers. This configuration leads to a band gap wavelength of  $1.6\,\mu\mathrm{m}$ . In figure 2 the resulting mode profile of the strip waveguide can be seen. Using this structure, we can achieve an optical confinement factor of 0.22 in the quantum wells.

#### III. FABRICATION

The SOI waveguide circuit was fabricated using 193 nm deep UV lithography and dry etching on a 8 inch SOI wafer in a CMOS pilot-line [3]. After dicing the wafer, the separate dies are cleaned in a Standard Clean-1 solution and a DVS-BCB polymer diluted with mesitylene (1BCB:5mes) is spin coated. In the mean time, the III-V dies are prepared by removal of the sacrificial InP/InGaAs layer pair. After evaporation of the mesitylene, the III-V dies are attached to the SOI die and cured at 250 C for one hour. Then the InP substrate of the attached III-V die is removed, using a combination of mechanical

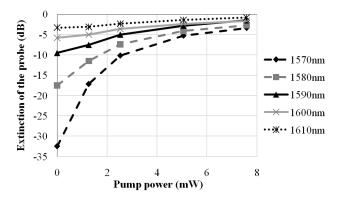

Fig. 3. Results for the CW pump-probe experiment. The different curves are for different probe wavelengths.

grinding and wet chemical etching using 3HCl: $\rm H_2O$  until the InGaAs etch stop layer is reached. The InGaAs etch stop layer is also removed by wet etching using  $\rm H_2SO_4$ : $\rm H_2O_2$ : $\rm 18H_2O$ . The remaining  $\rm 100\,nm$  stack is then covered with a  $\rm 50\,nm$  SiO<sub>2</sub> hard mask and patterned in III-V strip waveguides using contact lithography. Dry etching of the hard mask and the III-V layer leaves the III-V strip waveguides.

#### IV. CHARACTERIZATION

### A. Continuous wave experiment

A continuous wave (CW) pump-probe experiment was performed on these devices. In this experiment, a probe beam is coupled together with a  $1545\,\mathrm{nm}$  pump beam in the device. Both the pump power and the probe wavelength are varied. Comparison of the transmission through the devices and the transmission in a reference SOI waveguide gives us a measure for the net gain that is achieved in the strip waveguides. The results for a  $100\,\mu\mathrm{m}$  long device are shown in figure 3. As the pump power is increased, there is a clear saturation of the absorption of the probe. However, net gain is not reached. This lack of gain can be attributed to thermal effects, which are caused by both non-radiative recombination of the generated carriers and free carrier absorption of the pump and probe beam.

## B. Pulsed Experiment

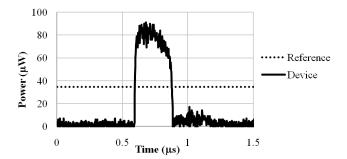

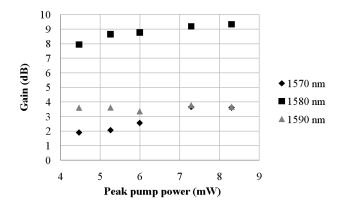

To rule out any thermal effects, the pump-probe experiment was repeated using a pulsed pump beam. By directly modulating a 1545 nm DFB laser, pulses of approximately  $0.5~\mu s$  could be created, with a period of  $10~\mu s$ . These are then amplified using a C-band EDFA after which the generated amplified spontaneous emission (ASE) was removed by a bandpass filter. This pump signal is then sent into the device, together with the CW probe beam. Because of the pulsed character of the pump beam, the probe beam is modulated. After extra amplification using a L-band EDFA and removal of the ASE and remaining pump power by a narrow band filter, the pulse profile of the probe beam is recorded using a high speed optical signal analyzer. In figure 4 a trace for the resulting pulse profile is shown and in figure 5 the achieved net gain is plotted as

Fig. 4. Trace of the resulting pulse profile of a 1570 nm probe beam for a peak pump power of 7.29 mW. The dashed line shows the transmitted power through the reference waveguide

Fig. 5. Net gain achieved in the  $100 \, \mu \text{m}$  long device for various wavelengths and pump powers.

a function of probe wavelength and pump power. From these results it can be seen that due to the high confinement in the quantum wells a very high net gain can be achieved at moderate pump powers. As expected the gain seems already saturated for powers less than 4.5 mW for the 1590 nm probe, while the gain still rises a little for shorter wavelengths. Due to absorption bleaching of the pump beam however, the gain will not increase much anymore with increasing pump power, unless the devices are pumped at a shorter wavelength.

#### V. CONCLUSION

We have demonstrated a net gain of over 8 dB in pulsed mode for a moderate pumping power in III-V membrane strip waveguides. Due to thermal effects there is no net gain in continuous wave mode however. In future work we will therefore focus on optimizing the design for lower thermal resistance.

### REFERENCES

- [1] G. Roelkens et al., Adhesive Bonding of InP/InGaAsP Dies to Processed Silicon-on-Insulator Wafers using DVS-bis-Benzocyclobutene, Journal of Electrochemical Society, vol. 153(12), pp. G1015-G1019, 2006.

- [2] G. Roelkens et al., III-V/silicon photonics for on-chip and inter-chip optical interconnects, Laser & Photonics reviews (invited), 2010.

- [3] www.epixfab.eu