# Adhesive Bonding of InP/InGaAsP Dies to Processed Silicon-On-Insulator Wafers using DVS-bis-Benzocyclobutene

G. Roelkens,<sup>a</sup> J. Brouckaert,<sup>a</sup> D. Van Thourhout,<sup>a</sup> R. Baets,<sup>a</sup> R. Nötzel,<sup>b</sup> and M. Smit<sup>b</sup>

<sup>a</sup>Department of Information Technology, Ghent University, Ghent, Belgium <sup>b</sup>Technical University Eindhoven, OED Group, Eindhoven, The Netherlands

The process of bonding InP/InGaAsP dies to a processed silicon-on-insulator wafer using sub-300 nm layers of DVS-bisbenzocyclobutene (BCB) was developed. The planarization properties of these DVS-bis-BCB layers were measured and an optimal prebonding die preparation and polymer precure are presented. Bonding quality and bonding strength are assessed, showing high-quality bonding with sufficient bonding strength to survive postbonding processing. © 2006 The Electrochemical Society. [DOI: 10.1149/1.2352045] All rights reserved.

Manuscript submitted June 20, 2006; revised manuscript received July 24, 2006. Available electronically October 9, 2006.

Silicon-on-insulator (SOI) is a material system that is gaining importance in semiconductor electronics industry for low power and high performance operation. Also in integrated optics it is an emerging technology platform. This is due to the fact that the refractive index contrast between the silicon waveguide core and the SiO<sub>2</sub> cladding is high ( $\Delta n \approx 2$ ). This allows making very compact integrated optical functions leading to large-scale integration of optical functions. Moreover, these optical components can be fabricated using standard complementary metal oxide semiconductor (CMOS) technology, improving the yield, reliability, and economy of scale. Although silicon is an interesting material for passive optical functions (optical filters, waveguiding, etc.) above 1.1 µm, where the material is transparent, it has an indirect bandgap and therefore is an inefficient light emitter. In order to integrate both active optical functions (laser emission, amplification, detection) and passive optical functions, III-V semiconductors with a direct bandgap need to be integrated on top of the passive SOI waveguide circuits. We focus in this paper on the integration of InP/InGaAsP heterostructures emitting at 1.55 µm on top of silicon-on-insulator waveguide circuits by means of a die to wafer bonding process, as shown in Fig. 1. Unprocessed InP/InGaAsP dies are bonded with its epitaxial layers down onto a processed SOI waveguide wafer, after which the InP substrate is removed. After substrate removal, the optoelectronic components can be fabricated in the bonded epitaxial layer.

Integration of two different material systems by means of a wafer bonding process can be done either using direct molecular bonding or adhesive bonding. Direct molecular bonding<sup>2</sup> relies on the van der Waals interaction between both surfaces. As this is a short-range force, sub-nm rms roughness of the surfaces is required.<sup>3</sup> Although this is obtainable on unprocessed SOI wafers using chemicalmechanical polishing (CMP)-and is the preferred way to fabricate SOI layer stacks-it is more difficult to obtain on the processed SOI waveguide circuits and on epitaxially grown InP/InGaAsP substrates. Therefore, in this work adhesive bonding was chosen to bond the III-V epi-structures on top of SOI waveguide circuits. One of the main advantages of adhesive bonding is that the surface quality that is required for bonding is less stringent as the polymer wets the surface and fills the troughs of the surface. It is also tolerant to particle contamination to some extent, and the topography of the surfaces to be bonded can be planarized by spin coating. Moreover, adhesive bonding processes are typically low-temperature processes, thereby reducing the stress due to the difference in thermal expansion of both materials. However, for the moment, little is known on the temperature stability and long-term stability of the bonding interface. It is also recognized that adhesive bonds are not hermetic seals.4

In literature, both thermosetting (spin-on glass,<sup>5</sup> polyimide,<sup>6</sup> benzocyclobutene,<sup>6</sup> etc.) and thermoplastic (PMMA,<sup>7</sup> SU-8,<sup>8</sup> etc.) polymers for adhesive bonding are described. For bonding using thermoplastic polymers, the post-bonding thermal budget is limited, which is a problem for the fabrication of the III-V devices

after bonding. For our application, 1,3-divinyl-1,1,3,3-tetramethyldisiloxane-bisbenzocyclobutene (DVS-bis-BCB) was chosen as a bonding agent. It has a low curing temperature (250°C) and a high glass transition temperature (350°C). The curing reaction starts by thermal opening of the benzocyclobutene, which undergoes a Diels-Alder reaction with other available DVS-bis-BCB molecules to form a three-dimensional network. No byproducts are created during curing, and shrinkage upon cure is small (<5%), which is advantageous for adhesive bonding.<sup>6</sup>

Depending on the application, different bonding layer thicknesses are desired. In this application, where optical coupling needs to occur between the III-V active device and an SOI waveguide, ultrathin bonding layers below 300 nm are needed.<sup>9</sup> These thin bonding layers are also advantageous to reduce the thermal resistance of the active III-V devices as adhesives typically have a low thermal conductivity ( $k_{\rm BCB} = 0.3 \text{ W/mK}$ ).<sup>10</sup>

### **DVS-bis-BCB** Adhesive Die to Wafer Bonding Process

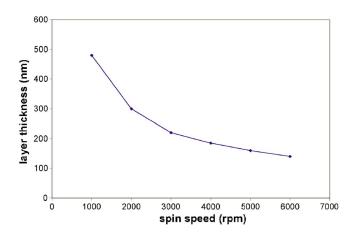

Commercially available B-staged DVS-bis-benzocyclobutene (Cyclotene 3022-35 from Dow Chemicals) was diluted using mesitylene (1,3,5-trimethylbenzene) to spin-coat ultrathin BCB layers. The thickness of Cyclotene 3022-35 diluted with 150% of mesitylene is shown in Fig. 2.<sup>11</sup> It was shown that defect-free films down to a few tens of nanometers in thickness can be obtained by simple solution casting.<sup>12</sup>

We evaluated the planarization properties of the ultrathin DVSbis-BCB layers on the SOI waveguide topography. The height of the topography is 220 nm while the density of the features varies over the wafer surface. Three different types of topography were investigated: 10  $\mu$ m wide trenches on a pitch of 30  $\mu$ m (topography A), 10  $\mu$ m wide trenches on a pitch of 120  $\mu$ m (topography B), and an isolated step in the topography. Preliminary measurements showed that spin coating of multiple layers with the same aggregate thickness of a single layer showed significantly better planarization properties than single-step spin coating. Therefore, we assessed the degree of planarization by using a double coating obtaining a total layer thickness of about 300 nm. Different combinations of spin coating and curing were tried and the degree of planarization was measured as shown in Table I.

Figure 1. (Color online) Heterogeneous integration of InP/InGaAsP on top of an SOI waveguide wafer by a die to wafer bonding process.

Figure 2. (Color online) Thickness of 2DVS-bis-BCB:3Mesitylene as a function of spin speed.

From these measurements, several conclusions can be drawn. First, it is clear that the planarization of the 30  $\mu$ m pitch features is better than that of the 120  $\mu$ m features. Second, the superior planarization properties of double spin-coated layers is clear: in the case of a 30  $\mu$ m pitch, even a higher degree of planarization can be obtained using an aggregate 300 nm BCB layer than with a single 760 nm thick BCB layer. The type of curing of the first spin-coated layer also plays a role. Soft-curing the BCB by slowly (1.6°C/min) ramping to 210°C (indicated by "ramped" in Table I) gives a higher degree of planarization than a rapid thermal anneal (2 min at 250°C) due to the reflow of the BCB in the case of slow ramping.

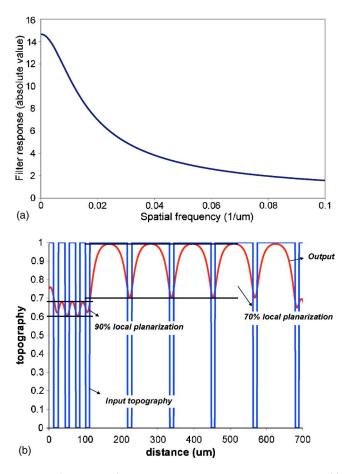

The planarizing properties of the spin-coating process can be better understood by treating the resulting topography after spin coating as the output of a low pass filter with the original topography function as an input. Measuring the topography on an isolated step after spin coating gives the step response of the filter and thereby its filter characteristic in the spatial frequency domain. This filter function is plotted in Fig. 3 for the case in which the first layer (150 nm) is slowly cured and the second layer (150 nm) is cured using rapid thermal annealing, together with an overlay of the original topography function and the planarization result of a topography containing 10  $\mu$ m trenches both on a 30 and 120  $\mu$ m pitch. A local degree of planarization of 90 and 70%, respectively, is obtained, which is consistent with the measured degree of planarization in Table I.

From these results, we designed the SOI topography to obtain a degree of planarization higher than 90% (meaning a residual nonplanarity below 20 nm). This residual nonplanarity can than be compensated for by the elastic deformation of the InP wafer and the partially cured DVS-bis-BCB. This can be achieved by adding dummy structures to the functional components in order to get a sufficient high-frequency content of the topography according to Fig. 3.

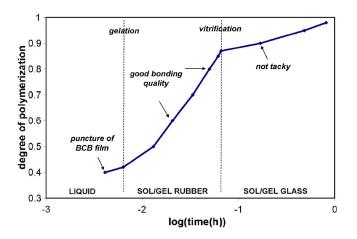

The optimum degree of polymerization of the DVS-bis-BCB layer prior to bonding was evaluated by bonding unprocessed flat wafer surfaces. A layer of 300 nm BCB was spin-coated on a Pyrex

Table I. Degree of planarization of thin DVS-bis-BCB layers on different types of topography.

|                                           | Top. A   | Top. B |

|-------------------------------------------|----------|--------|

| 150 nm BCB (ramped)                       | 0.84     | 0.66   |

| 150 nm BCB (ramped) + 150 nm BCB (ramped) | 0.95     | 0.8    |

| 150 nm BCB (ramped)                       | 0.91     | 0.75   |

| + 150 nm BCB (RTA)                        |          |        |

| Thick BCB layer                           | 0.925    | 0.945  |

|                                           | (760 nm) | (1 µm) |

Figure 3. (Color online) Transfer function of the spin coating process (a) and resulting planarization simulation (b).

host wafer and placed on a hot plate in a nitrogen environment at 250°C to evaporate the mesitylene solvent and partially cure the BCB. The degree of polymerization vs time is depicted in Fig. 4.<sup>13</sup> Subsequently InP dies were bonded (using a process that is described later) and the wafer stack was cured at 250°C for 1 h. The bonding quality was assessed by optical inspection through the Pyrex substrate. When the degree of polymerization of the DVS-bis-BCB is too high, it is not tacky any more and the bonding fails. When the BCB is still liquid, attaching the InP dies can puncture the

**Figure 4.** (Color online) Degree of polymerization vs time at 250°C (Ref. 13) and the relation with the quality of the bond.

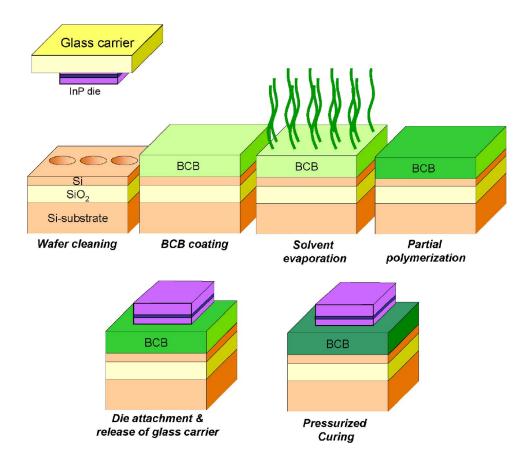

Figure 5. (Color online) Overview of the InP/InGaAsP die to wafer bonding process.

very thin DVS-bis-BCB layer, thereby reducing the bonded area, and this results in a lift-off of the bonded film during InP substrate removal. Best results were obtained when the BCB was in the sol/gel rubber phase. Nearly perfect bonding was obtained as the film can deform elastically and is still tacky.

As described below, from these experiments we developed a process to bond InP/InGaAsP heterostructure dies to a processed SOI substrate. Before bonding, the SOI waveguide substrate, with a topography designed for good planarization, is cleaned using an SC-1 solution ( $1NH_3:4H_2O_2:20H_2O$ ) at 70°C. This surface treatment lifts off particles from the surface and renders the surface hydrophilic. After surface cleaning, adhesion promoter AP-3000 from Dow Chemicals is applied. Mesitylene diluted Cyclotene 3022-35 is spincoated at 5000 rpm on the SOI and is soft-cured ( $210^{\circ}C$  for 40 min, ramped at  $1.6^{\circ}C$ /min). Subsequently, a second layer is spin-coated at 5000 rpm and undergoes a rapid thermal annealing for 2 min at 250°C, thereby increasing the degree of polymerization into the optimal region for bonding. Both curing steps are performed in a nitrogen environment to prevent the oxidation of the DVS-bis-BCB.

The cleaved InP/InGaAsP dies (with a size ranging from a few  $mm^2$  to 1 cm<sup>2</sup>) are temporarily attached to a Pyrex carrier using a thermoplastic photoresist. The surfaces are cleaned by removing a sacrifial InP and InGaAs layer using 3HCl:H<sub>2</sub>O and 1H<sub>2</sub>SO<sub>4</sub>:3H<sub>2</sub>O<sub>2</sub>:1H<sub>2</sub>O, respectively. This cleaning step removes the hydrocarbon contamination and lifts off the particles on the dies (mainly from the cleaving operation). The InP surface is conditioned for an optimal bonding strength by dipping in 1HF:10H<sub>2</sub>O (as will be shown in the subsection on characterization of the bonded layer stack). This surface treatment renders the InP surface hydrophilic.<sup>14</sup>

The InP dies are bonded in a vacuum environment to avoid the inclusion of air at the bonding interface. The bonding is performed at 150°C in order to detach the InP dies from the Pyrex carrier as the thermoplastic photoresist starts to flow at 150°C and the stack is

cured for 1 h at  $250^{\circ}$ C under a uniform pressure of 300 kPa in a nitrogen environment. The bonding sequence is graphically depicted in Fig. 5.

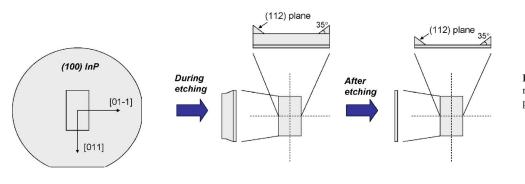

After bonding, the InP substrate of the bonded die is removed by mechanical grinding until about 80  $\mu$ m of the substrate remains, which is then chemically removed using 3HCl:H<sub>2</sub>O until an InGaAs etch stop layer is reached. Due to the anisotropic etching of the InP substrate using HCl, the (112) plane is exposed in the [011] direction, forming an angle of about 35 degrees with the surface, as is shown in Fig. 6. This is due to the fact that HCl does not etch an exposed (01-1) plane.<sup>15</sup> This can be circumvented by using a HCl:HNO<sub>3</sub> etching mixture that etches isotropically but is nonselective. Therefore, the final etching step always has to be a selective (and anisotropic) etch to the InGaAs etch stop layer. Another option is to saw the InP dies instead of cleaving them, thereby not exposing a single crystallographic plane. This might, however, introduce blisters at the epitaxial layer side, which can inhibit good bonding. On the other two faces of the die, the epitaxial layer can be slightly undercut by the HCl etching.

## **Characterization of Bonded Layer Structures**

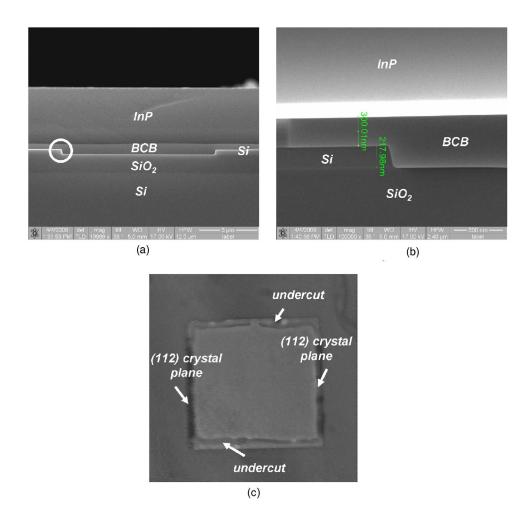

The die-to-wafer bonded structures were characterized on bonding quality and bonding strength. The bonding quality was assessed by scanning acoustic microscopy (SAM) revealing no delamination at the bonding interface. The resolution of this method is, however, limited to about 10  $\mu$ m. Infrared transmission inspection, optical inspection by bonding on a Pyrex host substrate, and SEM crosssection imaging were also performed, not revealing any bonding defects. A cross section and SAM top view image of a bonded layer structure after InP substrate removal is shown in Fig. 7.

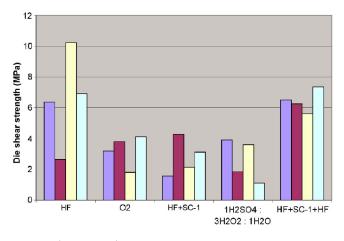

The bonding strength was assessed by performing die shear tests on the bonded samples. 25 mm<sup>2</sup> InP dies with different surface conditioning were bonded to a silicon host substrate and the shear force Journal of The Electrochemical Society, 153 (12) G1015-G1019 (2006)

**Figure 6.** (Color online) InP substrate removal and the revealing of the (112) plane by anisotropic HCl etching.

needed to detach the InP dies was measured. The results are depicted in Fig. 8, in which the die shear strength of 25 mm<sup>2</sup> InP dies that were bonded using a 300 nm DVS-bis-BCB layer is compared for various treatments of the InP surface prior to bonding. From these results it is clear that the HF treatment before bonding gives the highest bonding strength and that this is due to a chemical change in the surface condition and not due to a particle removal effect. This can be seen by comparing the results for the HF, HF + SC - 1, and HF + SC - 1 + HF maximum shear stress. For comparison, the influence of an O<sub>2</sub>-plasma (formation of oxides on the InP surface) and the influence of a 1H<sub>2</sub>SO<sub>4</sub>:3H<sub>2</sub>O<sub>2</sub>:1H<sub>2</sub>O surface treatment (for etching the sacrificial InGaAs layer) are also shown. The critical adhesion energy of the bonded stack was measured using the Maszara razor blade method.<sup>16</sup> It increased from 0.2 J/m<sup>2</sup>

of 300 nm. Typically, a 5  $J/m^2$  bonding energy is needed to survive the post-bonding processing steps (i.e., the mechanical grinding of the InP substrate).<sup>17</sup>

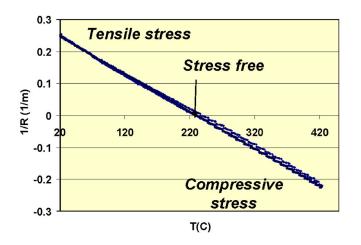

The stress induced in the bonded stack was measured by evaluating the wafer stack curvature as a function of temperature. The measurement results are plotted in Fig. 9. The temperature was ramped from 20 to 420°C at a rate of 5°C/min and then ramped back to room temperature. Little or no hysteresis can be seen and a linear relation is obtained as expected for elastic materials. The point of zero stress lies around 230°C. This is the point where the BCB fixes the InP die and the SOI substrate to form a rigid stack and lies close to the curing temperature of 250°C. The residual strain in the InP/InGaAsP epilayer at room temperature after substrate removal is therefore tensile. Strain levels are, however, below 0.05% in the

Figure 7. (Color online) Cross section (a,b) and SAM top view image (c) of a bonded layer structure. The SOI wave-guide layer, BCB bonding layer, and InP/InGaAsP layer are clearly distinguishable.

Figure 8. (Color online) Maximum shear force that can be applied to a bonded 25 mm<sup>2</sup> InP die bonded using 300 nm of DVS-bis-BCB.

InP/InGaAsP thin film after substrate removal, which is sufficiently low to prevent changes in the light emission properties of the InP/InGaAsP layer.

#### Applications

InP/InGaAsP die to SOI wafer bonding was demonstrated for the integration of III-V Fabry-Perot laser diodes, MSM photodetectors,

Figure 9. (Color online) Measurement of the wafer curvature as a function of temperature. The nature of the stress in the InP/InGaAsP layer is also added.

and pin-photodetectors<sup>18,19</sup> on top of SOI waveguide circuits. While not yet demonstrated, this technology is equally attractive for the integration of III-V modulators, optical amplifiers, and microlasers on top of SOI waveguide circuits.

#### Conclusions

An integration process of InP/InGaAsP dies on top of silicon-oninsulator waveguide circuits by means of DVS-bisbenzocyclobutene adhesive bonding was developed. High-quality InP/InGaAsP epitaxial layer structures bonded to SOI were obtained and the bonding strength and quality were evaluated. First demonstrators of this technology for the fabrication of InP/InGaAsP active optical devices on top of SOI have been made, but the applicability of this generic technology reaches much further.

Ghent University assisted in meeting the publication costs of this article.

#### References

- 1. W. Bogaerts and R. Baets, J. Lightwave Technol., 23, 401 (2005).

- Q.-Y. Tong and U. Gosele, Semiconductor Wafer Bonding—Science and Technology, The Electrochemical Society Series, Wiley Interscience (1999).

- 3. N. Miki and S. M. Spearing, J. Appl. Phys., 94, 6800 (2003).

- F. Niklaus, G. Stemme, J. Q. Lu, and R. J. Gutmann, J. Appl. Phys., 99, 031101 (2006).

- H. C. Lin, K. L. Chang, G. W. Pickrell, K. C. Hsieh, and K. Y. Cheng, J. Vac. Sci. Technol. B, 20, 752 (2002).

- F. Niklaus, P. Enoksson, E. Kalvesten, and G. Stemme, J. Micromech. Microeng., 11, 100 (2001).

- 7. W. P. Eaton, S. H. Risbud, and R. L. Smith, Appl. Phys. Lett., 65, 439 (1994).

- F. J. Blanco, M. Agirregabiria, J. Garcia, J. Berganzo, M. Tijero, M. T. Arroyo, J. M. Ruano, I. Aramburu, and K. Mayora, *J. Micromech. Microeng.*, 14, 1047 (2004).

- G. Roelkens, D. Van Thourhout, and R. Baets, J. Lightwave Technol., 23, 3827 (2005).

- I. Christiaens, G. Roelkens, K. De Mesel, D. Van Thourhout, and R. Baets, J. Lightwave Technol., 23, 517 (2005).

- G. Roelkens, D. Van Thourhout, and R. Baets, *Electron. Lett.*, **41**, 561 (2005).

L. L. Chua, P. Ho, H. Sirringhaus, and R. Friend, *Appl. Phys. Lett.*, **84**, 3400 (2004).

- P. E. Garrou, R. H. Heistand, M. G. Dibbs, T. A. Mainal, C. E. Mohler, T. M. Stokich, P. H. Townsend, G. M. Adema, M. J. Berry, and I. Turlik, *Trans. Components Hybrids Manufacturing Technol.*, **16**, 46 (1993).

- Y. Sun, Z. Liu, F. Machuca, P. Pianetta, and W. E. Spicer, J. Appl. Phys., 97, 162 (2005).

- L. A. Coldren, K. Furuya, B. I. Miller, and J. A. Rentschler, *Electron. Lett.*, 18, 235 (1982).

- W. P Maszara, G. Goetz, A. Caviglia, and J. B. Mckitterick, J. Appl. Phys., 64, 4943 (1988).

- Y. Kwon, J. Seok, J. Q. Lu, T. S. Cale, and R. J. Gutmann, J. Electrochem. Soc., 153, G347 (2006).

- G. Roelkens, J. Brouckaert, D. Taillaert, P. Dumon, W. Bogaerts, D. Van Thourhout, R. Baets, R. Notzel, and M. Smit, *Opt. Express*, 13, 10102 (2005).

- G. Roelkens, J. Brouckaert, S. Verstuyft, J. Schrauwen, D. Van Thourhout, and R. Baets, Paper Th82 presented at Group IV Photonics 2006 Conference, Ottawa, ON, Canada (2006).