# IN FACULTY OF ENGINEERING

### III-V-on-Si SOAs and DFB/DBR Lasers Realised Using Micro-Transfer Printing

#### Bahawal Haq

Doctoral dissertation submitted to obtain the academic degree of Doctor of Photonics Engineering

Supervisors Prof. Günther Roelkens, PhD - Prof. Geert Morthier, PhD

Department of Information Technology Faculty of Engineering and Architecture, Ghent University

June 2021

ISBN 978-94-6355-490-9 NUR 965 Wettelijk depot: D/2021/10.500/38

### Members of the Examination Board

#### Chair

Prof. Em. Hendrik Van Landeghem, PhD, Ghent University

#### Other members entitled to vote

Prof. Zeger Hens, PhD, Ghent University Prof. Yuqing Jiao, PhD, Technische Universiteit Eindhoven, the Netherlands Prof. Geert Van Steenberge, PhD, Ghent University Prof. Xin Yin, PhD, Ghent University

#### Supervisors

Prof. Günther Roelkens, PhD, Ghent University Prof. Geert Morthier, PhD, Ghent University

## Dankwoord

The meticulousness required to write this section makes it more challenging than the rest of the thesis and I hope that I will not forget to mention anyone. In retrospect, the first time I studied the field of optics and photonics was in my undergraduate in Pakistan. I was fascinated by photonics from the start. It made me realize how powerful nature and its processes can be. Light, as it may seem ordinary and mundane to a layman, is one of the most powerful tools of nature. It never fails to amaze you, the deeper you study it, the more you want to learn about it. By the time, I finished my undergraduate, I had already made up my mind to pursue a Ph.D. degree in the field of photonics. Now that I think in retrospect, I am thankful to my teachers who played an important role in developing interest in the field of photonics and told us about various universities and institutes that offer education in this field. I liked the idea of studying abroad, traveling, and living in a different country. I remember applying to many master's degree programs and luckily, I got admission in a few of them with scholarships. I am grateful to my teachers who taught high-quality courses in my master's degree which helped me a lot during the Ph.D. Moreover, I am also grateful to my master's degree supervisor Prof. Rasras for introducing me to the field of silicon photonics.

The first time I googled IMEC was at the beginning of my master's degree. At that time, I already knew about Ghent University and the Photonics research group (PRG) because of the European master in science program. Immediately after finishing my master's, I started applying for Ph.D. positions. One day, a good friend of mine Ali Raza, who also did his Ph.D. in the PRG, sent me an open Ph.D. position in the group. I applied and was lucky enough to get accepted for the Ph.D. position. I am very grateful to Prof. Roelkens for giving me this opportunity. It would be an understatement to say that the last four years, working in this group and living in the beautiful city of Gent, were one of the most formative years for me, both intellectually and interpersonally. It has been a worthwhile experience of doing a Ph.D. under the supervision of Prof. Roelkens. Your patience and concern for your students are highly admirable. Moreover, it is needless to say that several times during the last four years, I was awestruck by your intelligence and the approach to solving problems. I wish that I would be able to develop this in myself in years to come. I have surely learned a lot from you and will continue the journey of life-long learning. I would also like to thank Prof. Morthier for providing valuable feedback and comments during the meetings and for the improvement of this thesis. I would also like to thank all my Ph.D. jury members: prof. Geert Van Steenberge, prof. Xin Yin, prof. Zeger Hens, and prof. dr. Yuqing Jiaon for providing valuable comments that helped to improve this thesis. I would also like to thank all other professors of the group for making it a complete package. The diversity, great organization, and camaraderie in our group makes it one of the best workplace. To be able to cultivate such a culture in a workplace is not an easy task and your efforts in this regard are highly commendable.

This Ph.D. work would not have been possible without the help and support from several colleagues, friends, and family. I was lucky to find several mentors in the group in the form of colleagues. In the first year of my Ph.D., Ruijun Wang was my go-to person whenever I had problems and questions. I don't know if he will ever read this but thank you for being kind and patient to me and for helping me at the start of my Ph.D. Afterward, when I became more active in the cleanroom, my go-to person changed to Jing Zhang. Thanks, Jing for being patient and always listening, and providing your valuable feedback to me. You also showed me how to process my first III-V SOA coupons and I am grateful for that. I am thankful to Muhammad Muneeb and Steven for helping me with processing and also for having fruitful discussions whenever it was needed in the cleanroom. I am also very grateful to Sulakshna Kumari for processing my Si chips and for helping me with SEM imaging multiple times. You were also very patient and never complained even though you had several tasks of your own. Your addition to the transfer-printing team was very valuable. I am also thankful to Kasper Van Gasse for helping me with the SOA paper, your feedback was very valuable. I would also like to thank Andreas and Grigorij for hands-on training on the micro-transfer printing tool. The most important people that were my life support in Gent: Abdul Rahim and Ali Raza. The time spent in Gent would have been difficult without you. Thank you for being amazing friends and for always being there when it was needed. I would also like to thank my office mates Chen, Daan,

Ruijun, Fabio, Grigorij, Sulakshna, Lukas, and Mi for the nice working environment and many discussions. I was often found chatting with Ali in his office, I would like to thank his office mates Alex, Mattias, Jasper, Paul, and Jing for not kicking me out of the office. Many thanks to several current and former members of the micro-transfer printing team: Jeroen, Camiel, Javad, Nayyera, Sarah, Nan, and Tom for valuable discussions during and after the meetings. Moreover, many other colleagues have helped and supported me in many ways during the last few years, I am thankful to all of you.

I would like to thank Ilse Van Royen, Mike, and Bert for helping with administrative issues. Kristien, thank you very much for the technical support for all these years. I am pretty sure there is not a single technical problem that you cannot solve. I would also like to thank Wim and Abdul for help related to simulation machines and licenses. Many thanks to Ilse and Ilse for the assistance related to conference-related planning and reimbursements and other issues related to imec. Michael and Jasper, many thanks for technical support related to measurement labs.

I made amazing friends while I was doing my master's in UAE. Fortunately, some of them also moved to Belgium in the last few years. Abdul Mannan, Noor, Nazeer, Mahmoud, and Juliana, I am very grateful to meet you and being in your company multiple times in the last four years. Thank you for giving me all the wonderful memories that I will cherish in the future. I am very lucky to have friends and family that might have been living on other continents but are always close to my heart. They are always there to listen, guide and help whenever it is needed. I can't name all of you here but I am grateful to have you in my life.

I am also thankful to several members of the Pakistani community living in Gent including Umar, shahid, Adnan, and many more for helping me on several occasions and for your valuable company over the last few years.

Finally, I am grateful to my parents for their unconditional love and support. It would not have been possible without you.

Gent, 18<sup>th</sup>May 2021 Bahawal Haq

# Table of Contents

| Da | nkwo   | oord                                              | i   |

|----|--------|---------------------------------------------------|-----|

| Ne | derla  | ndse samenvatting                                 | XXV |

| En | ıglish | summary x                                         | XXV |

| 1  | Intr   | oduction                                          | 1   |

|    | 1.1    | Applications                                      | 2   |

|    |        | 1.1.1 Photonics and optical interconnects         | 2   |

|    |        | 1.1.2 Spectroscopy and sensing                    | 3   |

|    |        | 1.1.3 Light detection and ranging (LiDAR)         | 6   |

|    | 1.2    | Silicon Photonics                                 | 8   |

|    |        | 1.2.1 Silicon-on-insulator PICs                   | 8   |

|    |        | 1.2.2 Heterogeneous III-V-on-Si integration       | 10  |

|    |        | 1.2.2.1 Direct or adhesive bonding                | 10  |

|    |        | 1.2.2.2 Direct epitaxial growth                   | 11  |

|    |        | 1.2.2.3 Regrowth on a bonding template            | 11  |

|    |        | 1.2.2.4 Flip-chip integration                     | 12  |

|    |        | 1.2.2.5 Micro-transfer printing                   | 13  |

|    | 1.3    | State-of-art heterogeneously integrated SOAs      | 14  |

|    |        | 1.3.1 Figures of Merit                            | 14  |

|    |        | 1.3.2 Review on III-V-on-Si SOAs                  | 15  |

|    | 1.4    | Publications in international journals            | 17  |

|    | 1.5    | Publications in international conferences         | 18  |

|    | Refe   | erences                                           | 20  |

| 2  | Ena    | bling micro-transfer printing of III-V-on-Si SOAs | 25  |

|    | 2.1    | Introduction to micro-transfer printing           | 25  |

|    | 2.2    | Working principle of micro-transfer printing      | 26  |

|    | 2.3    | Process flow for micro-transfer printing SOAs     | 28  |

|    |        | 2.3.1 Micro-transfer-printing process             | 31  |

|   |      | 2.3.2    | Processing issues and fixes                       | 33 |

|---|------|----------|---------------------------------------------------|----|

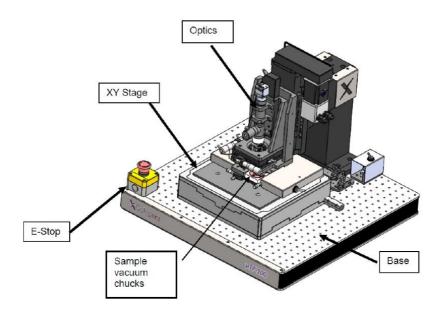

|   | 2.4  | Micro-t  | transfer printing tool                            | 34 |

|   | 2.5  |          | tic alignment-tolerant taper design               | 36 |

|   |      | 2.5.1    | 400 nm thick Si with 180 nm etch-depth            | 36 |

|   |      | 2.5.2    | Design for imec iSIPP50G platform                 | 41 |

|   | 2.6  |          | sion                                              | 44 |

|   | Refe |          |                                                   | 46 |

| 3 | Mic  | ro-trans | fer-printed C-band SOAs                           | 49 |

|   | 3.1  | Introdu  | ction                                             | 49 |

|   | 3.2  | Design   | of the III-V-on-Si SOA                            | 51 |

|   | 3.3  | Fabrica  | tion                                              | 53 |

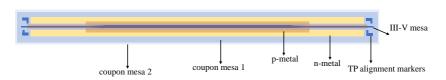

|   |      | 3.3.1    | Lithography mask design for processing on InP die | 53 |

|   |      | 3.3.2    | SOA processing on the III-V source wafer          | 53 |

|   |      | 3.3.3    | SOI processing                                    | 58 |

|   |      |          | 3.3.3.1 e-beam lithography                        | 58 |

|   |      |          | 3.3.3.2 Patterning of SOI                         | 59 |

|   |      | 3.3.4    | Micro-transfer printing of SOAs                   | 60 |

|   |      | 3.3.5    | Post-processing of the III-V/SOI structures       | 61 |

|   | 3.4  | Device   | characterization                                  | 62 |

|   | 3.5  |          | sion                                              | 69 |

|   | Refe | rences . |                                                   | 70 |

| 4 | Mic  | ro-trans | fer-printed DFB lasers                            | 73 |

|   | 4.1  | Introdu  | ction                                             | 73 |

|   | 4.2  |          | micro-transfer-printed DFB lasers                 | 74 |

|   |      | 4.2.1    | Design of DFB laser                               | 74 |

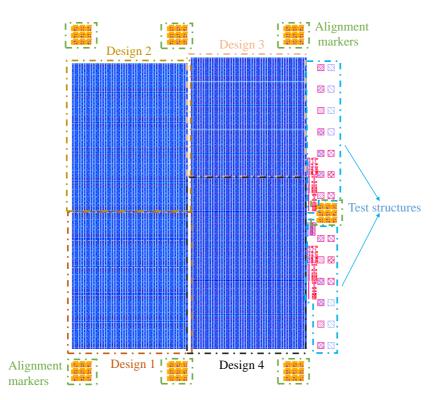

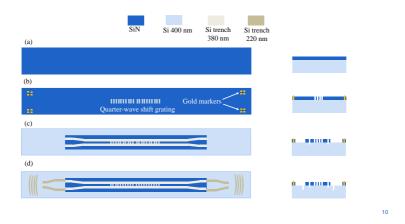

|   |      | 4.2.2    | SOI lithography mask layout                       | 75 |

|   |      | 4.2.3    | Fabrication                                       | 78 |

|   |      |          | 4.2.3.1 SOI processing                            | 78 |

|   |      |          | 4.2.3.2 III-V processing on InP                   | 81 |

|   |      | 4.2.4    | Micro-transfer printing process                   | 81 |

|   | 4.3  | Charact  | terization                                        | 83 |

|   | 4.4  |          | micro-transfer-printed DFB lasers                 | 86 |

|   |      | 4.4.1    | Design                                            | 86 |

|   |      | 4.4.2    | Fabrication                                       | 91 |

|   |      | 4.4.3    | Characterization                                  | 93 |

|   | 4.5  | Conclu   | sion                                              | 96 |

|   | Refe | rences.  |                                                   | 97 |

| 5 | Mic                     | ro-transfer-printed DBR lasers        | 99  |  |  |

|---|-------------------------|---------------------------------------|-----|--|--|

|   | 5.1                     | Introduction                          | 99  |  |  |

|   | 5.2                     | Device Design                         | 100 |  |  |

|   |                         | 5.2.1 Single-mode DBR laser design    | 101 |  |  |

|   | 5.3                     | Fabrication                           | 102 |  |  |

|   |                         | 5.3.1 Micro-transfer-printing process | 102 |  |  |

|   | 5.4                     | Device characterization               | 104 |  |  |

|   | 5.5                     | Misalignment measurement              | 108 |  |  |

|   | 5.6                     | Conclusion                            | 112 |  |  |

|   | Refe                    | erences                               | 114 |  |  |

| 6 | Conclusions and outlook |                                       |     |  |  |

|   | 6.1                     | Conclusion                            | 117 |  |  |

|   | 6.2                     | Outlook                               | 118 |  |  |

# List of Figures

| 1 | Schematische voorstelling van het micro-transfer-printproces<br>van geprefabriceerde SOA-coupons                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|---|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

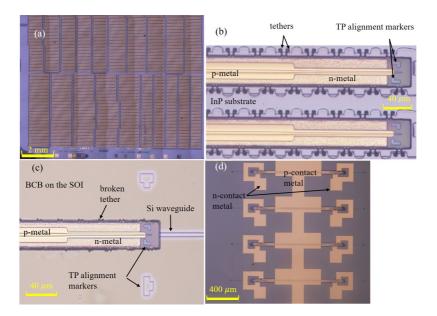

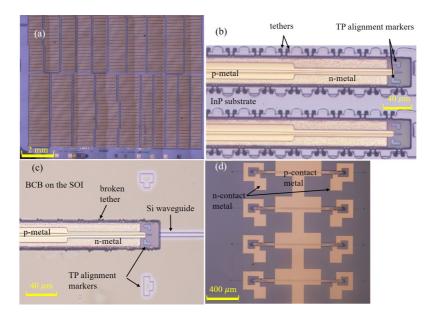

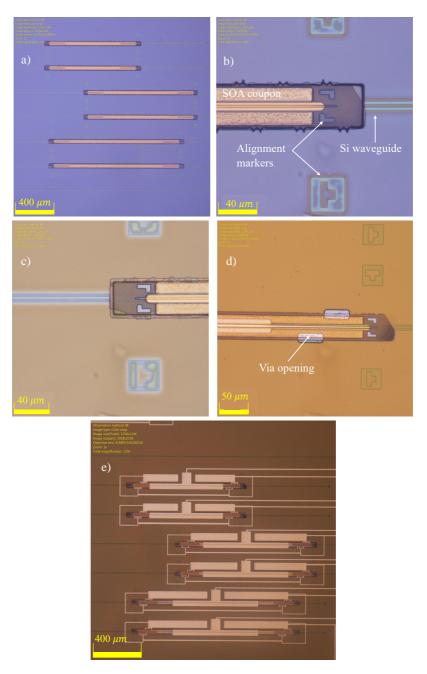

| 2 | Microscoopbeeld van a) verwerkte SOA-coupons op het<br>InP-substraat, b) twee SOA-coupons van (a) waarop wordt<br>ingezoomd, c) geprinte SOA-coupon op een Si-golfgeleider,<br>en d) III-V-on-Si SOA's met metaalcontacten                                                                                                                                                                                                                                                                                                                                                                                                                            |

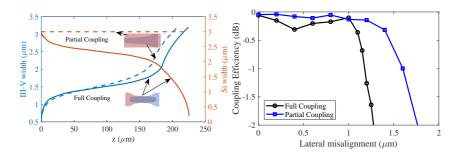

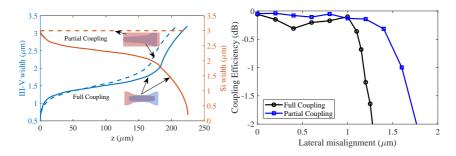

| 3 | (links) De III-V en Si adiabatische koppelstructuur in de<br>lengterichting. De blauwe lijn en de linker verticale as<br>stellen de III-V adiabatische conische vorm voor de gedeel-<br>telijke en volledige koppelingsontwerpen. De rode lijn en<br>de rechter verticale as representeren de adiabatische conis-<br>che vorm van Si en de breedte van de Si golfgeleider in<br>het geval van respectievelijk volledige koppeling en gedeel-<br>telijke koppeling; (rechts) De gesimuleerde koppelingsef-<br>ficiëntie van de adiabatische structuren voor de ontwerpen<br>voor gedeeltelijke en volledige koppeling versus de laterale<br>uitlijning |

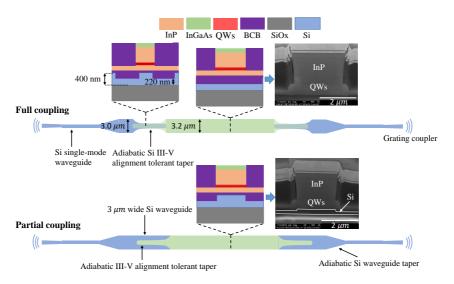

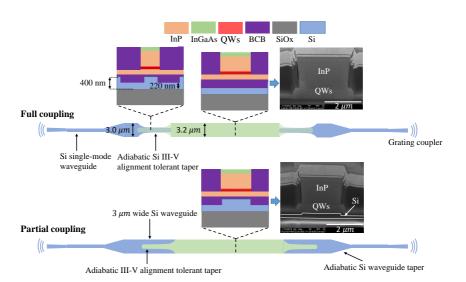

| 4 | Schema's en FIB-doorsneden die het ontwerp van de volledige<br>koppeling en gedeeltelijke koppeling voor III-V-op-Si SOA's<br>illustreren                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

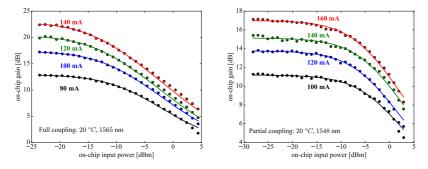

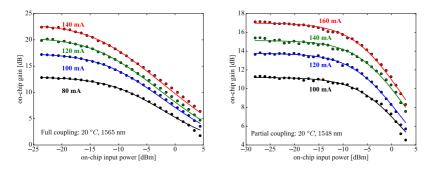

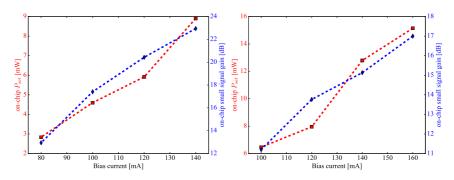

| 5 | Variatie van de versterking op de chip met het ingangsver-<br>mogen op de chip voor verschillende instelstromen, (links)<br>voor het ontwerp met volledige koppeling bij 1565 nm,<br>(rechts) voor het ontwerp met de gedeeltelijke koppeling<br>bij 1548 nm                                                                                                                                                                                                                                                                                                                                                                                          |

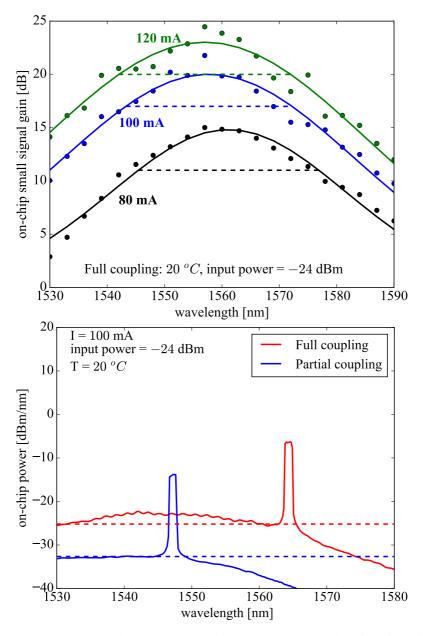

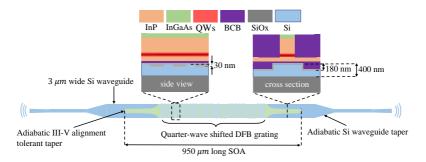

| 6  | Schematische voorstelling van het ontwerp van de DFB-<br>laser met aanzicht in dwarsdoorsnede van de adiabatische<br>structuur en het zijaanzicht van het DFB-rooster. SEM-<br>afbeeldingen van a) overgang tussen DFB sectie en passieve<br>siliciumgolfgeleider, b) longitudinale dwarsdoorsnede van<br>het DFB-rooster en c) het modeprofiel in de versterkings-<br>sectie.                                                                                                                                                                                       | xxxi    |

|----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|

| 7  | (boven) Golfgeleider-gekoppeld uitgangsvermogen (enkel-<br>zijdig) als functie van stroom voor verschillende bedrijf-<br>stemperaturen en de stroom-spanningskarakteristiek, (on-<br>der) Gemeten spectrum (0,05 nm resolutie) bij 90 mA en                                                                                                                                                                                                                                                                                                                          | xxxii   |

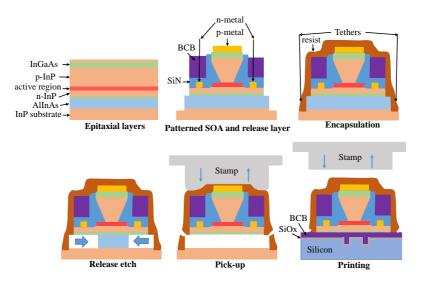

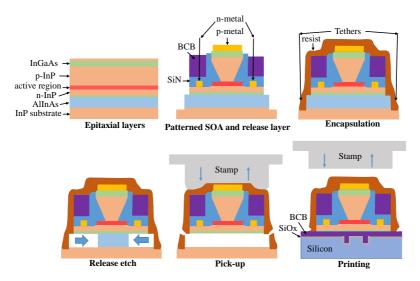

| 8  | Schematic illustrating the micro-transfer printing process of pre-processed SOA coupons                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | xxxvi   |

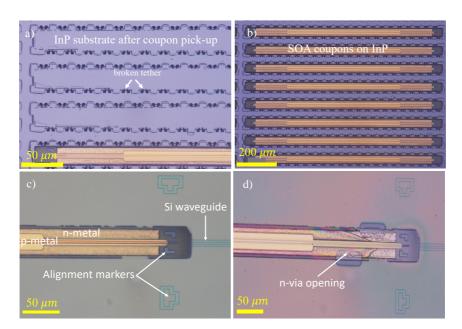

| 9  | Microscope image of a) processed SOA coupons on the<br>InP substrate, b) two zoomed-in SOA coupons from (a),<br>c) micro-transfer-printed SOA coupon on a Si waveguide,<br>and d) III-V-on-Si SOAs with contact pads                                                                                                                                                                                                                                                                                                                                                 | xxxvii  |

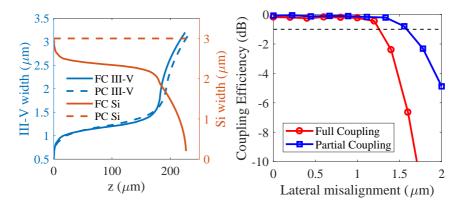

| 10 | (left) The III-V and Si adiabatic taper width variation along<br>its length. The blue line and the left vertical axis repre-<br>sents the III-V adiabatic taper shape for the partial and full<br>coupling designs. The red line and the right vertical axis<br>represents the Si adiabatic taper shape and Si waveguide<br>width in the case of full coupling and partial coupling, res-<br>pectively; (right) The simulated coupling efficiency of the<br>adiabatic taper structures for the partial and full-coupling<br>designs versus the lateral misalignment. | xxxviii |

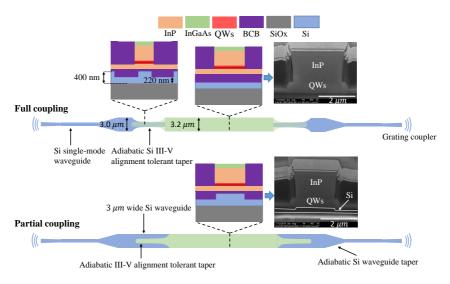

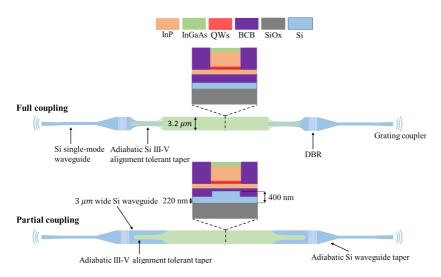

| 11 | Schematics and FIB cross-sections illustrating the design of the full-coupling and partial-coupling III-V-on-Si SOAs.                                                                                                                                                                                                                                                                                                                                                                                                                                                | xxxix   |

| 12 | Variation of the on-chip gain with the on-chip input power<br>for various bias currents, (left) for the full-coupling design<br>at 1565 nm, (right) for the partial-coupling design at 1548 nm.                                                                                                                                                                                                                                                                                                                                                                      | .xxxix  |

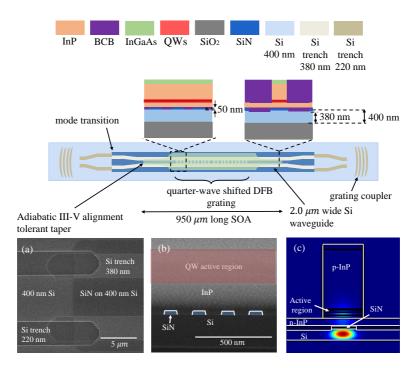

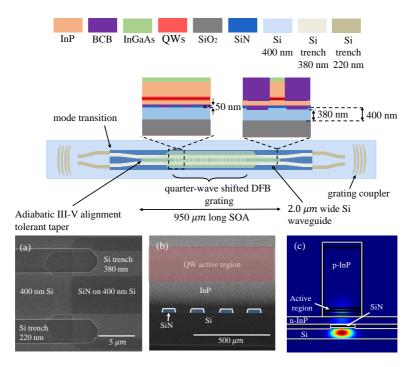

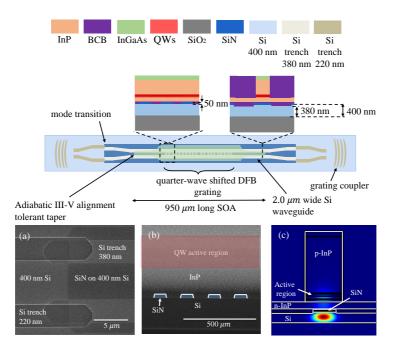

| 13 | Schematic illustrating the design of the DFB laser with cross-<br>section view of the adiabatic taper and the side view of the<br>DFB grating. SEM images of a) mode transition, b) longi-<br>tudinal cross-section of the DFB grating and c) the mode<br>profile in the gain section are also shown                                                                                                                                                                                                                                                                 | xli     |

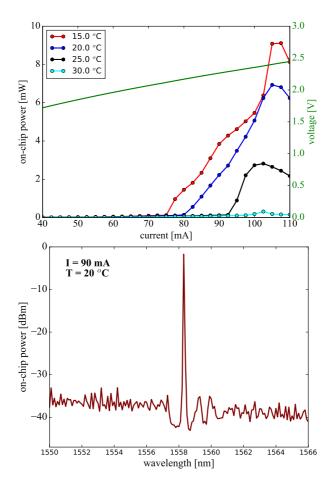

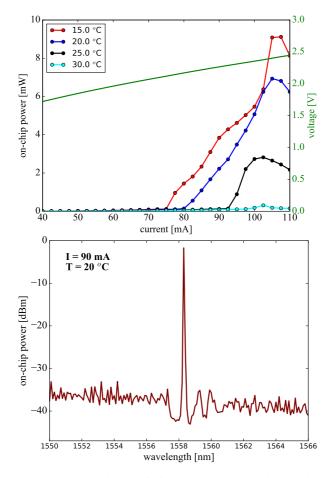

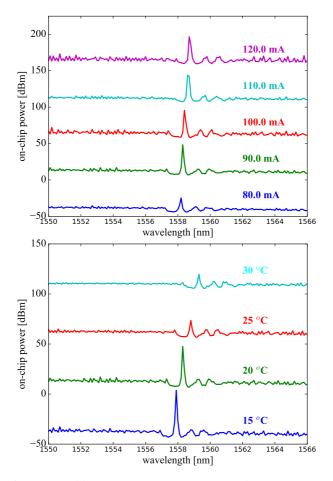

| 14  | (top) Waveguide-coupled output power (single-sided) as a function of bias current for various operating temperatures and the current-voltage characteristic, (bottom) Measured spectrum at 0.05 nm resolution, at 90 mA and at 20 $^{\circ}$ C operating temperature.                              | xlii |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

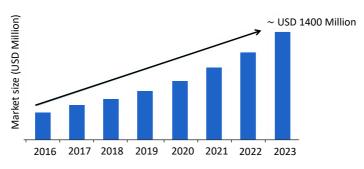

| 1.1 | Expected PICs market growth, reproduced from [1]                                                                                                                                                                                                                                                   | 2    |

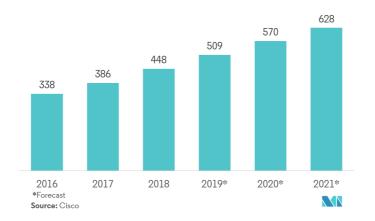

| 1.2 | Predicted two-fold increase in hyper-scale data centers from 2016 to 2021 [4]                                                                                                                                                                                                                      | 3    |

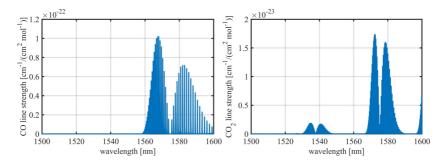

| 1.3 | Absorption spectra of pure CO and $CO_2$ (100 % by volume)<br>in the NIR spectral region at 273 K and 1 atm pressure                                                                                                                                                                               | 5    |

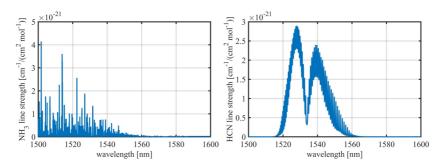

| 1.4 | Absorption spectra of pure $NH_3$ and $HCN$ (100 % by volume) in the NIR spectral region at 273 K and 1 atm pressure.                                                                                                                                                                              | 5    |

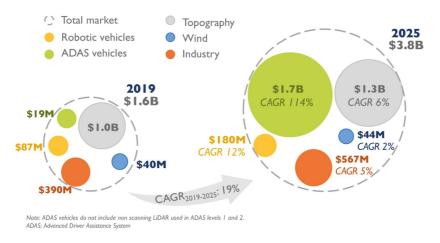

| 1.5 | LiDAR market forecast by Yole development [6]                                                                                                                                                                                                                                                      | 6    |

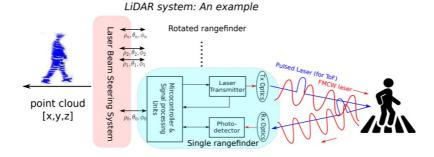

| 1.6 | A conceptual diagram of a LiDAR system [7]                                                                                                                                                                                                                                                         | 7    |

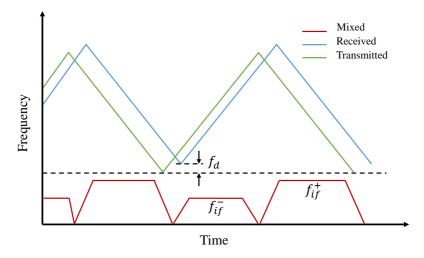

| 1.7 | An example of received, transmitted and mixed signal in                                                                                                                                                                                                                                            | ,    |

|     | coherent LiDAR system.                                                                                                                                                                                                                                                                             | 8    |

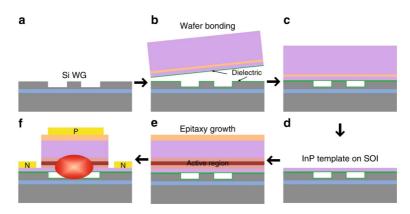

| 1.8 | Process flow schematic of regrowth on a bonding template                                                                                                                                                                                                                                           |      |

|     | III-V-on-Si integration [24]                                                                                                                                                                                                                                                                       | 12   |

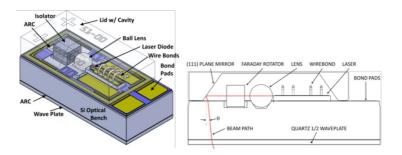

| 1.9 | Micro-optical bench packaging from Luxtera [29]                                                                                                                                                                                                                                                    | 13   |

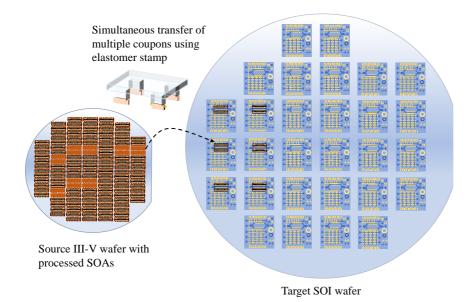

| 2.1 | Schematic illustrating the micro-transfer printing of four                                                                                                                                                                                                                                         | 26   |

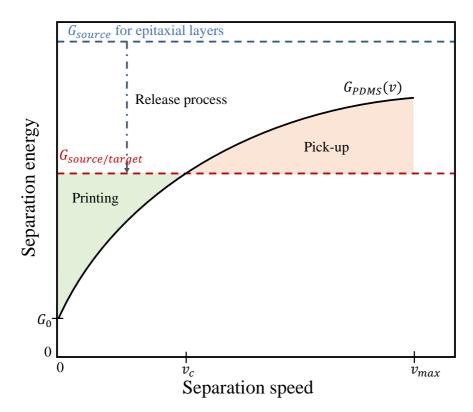

| 2.2 | SOA coupons to a SOI wafer using a PDMS stamp Schematic illustrating the dependence of separation energy on the separation velocity of the PDMS stamp. The blue dotted line shows the high separation energy of semicon-ductor epitaxial layers. For simplicity we assume that G <sub>source</sub> | 26   |

|     | $= G_{target} \text{ in this graph.} \dots \dots$                                                                                                                                            | 27   |

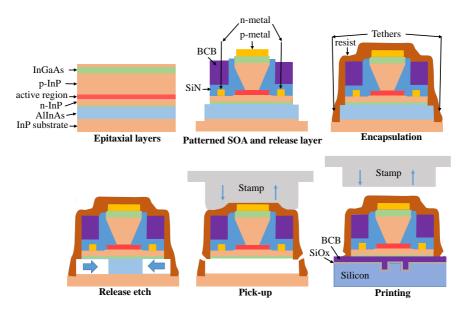

| 2.3 | Schematic illustrating the micro-transfer printing process                                                                                                                                                                                                                                         | _,   |

|     | of processed SOA coupons                                                                                                                                                                                                                                                                           | 30   |

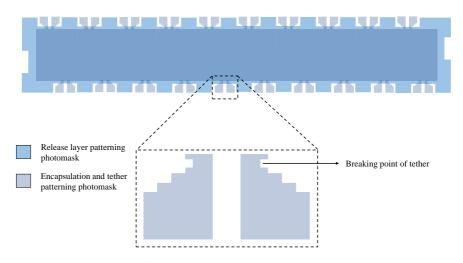

| 2.4 | Schematic illustrating the photomask used to pattern the release layer and to encapsulate the device. The zoom-in                                                                                                                                                                                  | 0.1  |

| 2.5 | schematic of the tether design is also depicted.                                                                                                                                                                                                                                                   | 31   |

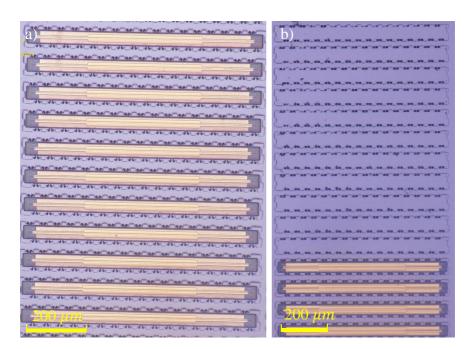

| 2.5 | a) Microscope image of the released SOA coupons, b) Mi-<br>croscope image of the sample after coupons have been picked-                                                                                                                                                                            |      |

|     | up                                                                                                                                                                                                                                                                                                 | 32   |

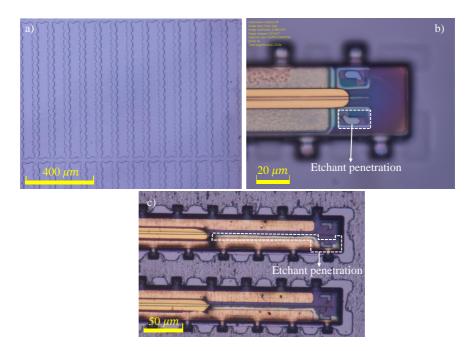

| 2.6 | (a) Microscope image of a failed release process, the coupons detached from the substrate. b) and c) Microscope image                                                                                                                                                                              |      |

|     |                                                                                                                                                                                                                                                                                                    |      |

|     | depicting the effects of $FeCl_3$ penetration in the SOA coupons.                                                                                                                                                                                                                                  | 33   |

xi

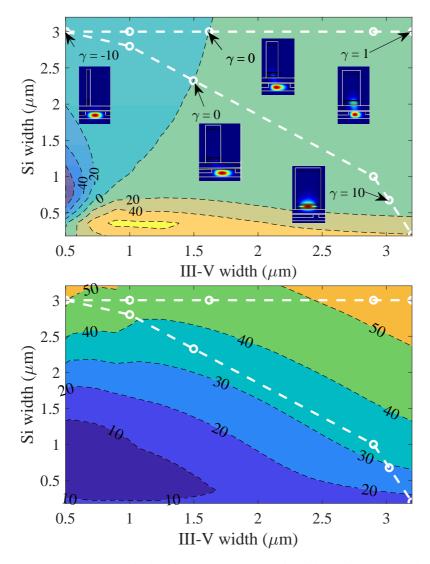

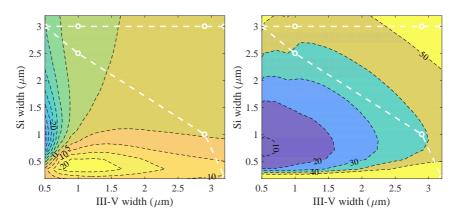

| 2.8  | (Top) Calculated map of $\gamma$ for several width combinations of the III-V and Si waveguide. The white dashed lines rep-                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |    |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|      | resent the trajectory of the points choosen to design the adiabatic tapers. The insets are the optical modal profiles found using simulations at $\gamma = -10$ (the optical mode is mostly confined in the Si waveguide), $\gamma = 0$ (this is the phase matching point at which the coupling takes place), $\gamma = 1$ (the optical mode is distributed unevenly in both Si and III-V waveguide), and $\gamma = 10$ (the optical mode is confined in the III-V waveguide) , (Bottom) Calculated map of $\kappa$ in mm <sup>-1</sup> for several width combinations of the III-V and Si waveguide. | 38 |

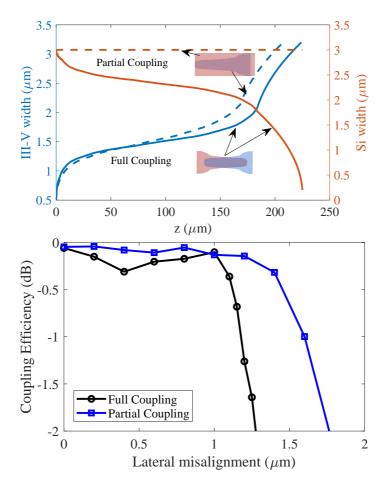

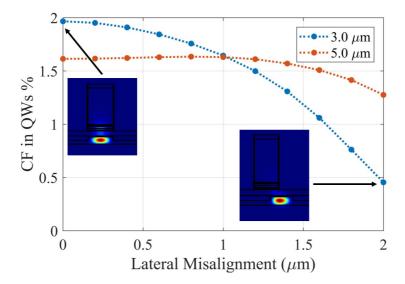

| 2.9  | (Top) The III-V and Si adiabatic taper width variation along<br>its length. The blue line and the left vertical axis represents<br>the III-V adiabatic taper shape for the partial and full cou-<br>pling designs. The red line and the right vertical axis repre-<br>sents the Si adiabatic taper shape and Si waveguide width<br>in the case of full coupling and partial coupling, respec-<br>tively; (Bottom) The simulated coupling efficiency of the<br>adiabatic taper structures for the partial and full-coupling<br>designs versus the lateral misalignment.                                | 40 |

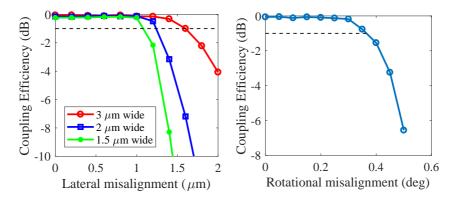

| 2.10 | (left) Calculated power coupling between full-coupling III-<br>V adiabatic taper design and Si waveguide of width 3.0 $\mu$ m,<br>2.0 $\mu$ m and 1.5 $\mu$ m, (right) Calculated coupling efficiency<br>against the rotational misalignment between III-V adiabatic<br>taper and Si waveguide.                                                                                                                                                                                                                                                                                                       | 41 |

| 2.11 | The change in confinement factor in QWs with the mis-<br>alignment variation for 3.0 $\mu$ m and 5.0 $\mu$ m Si waveguide<br>width, insets illustrate the mode profile at zero and 2.0 $\mu$ m<br>misalignment.                                                                                                                                                                                                                                                                                                                                                                                       | 42 |

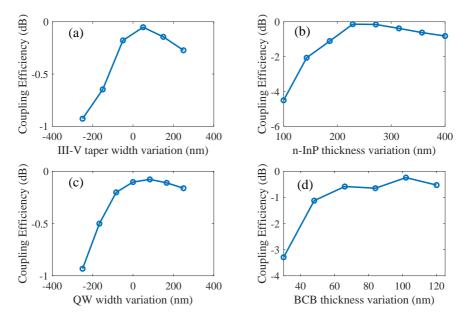

| 2.12 | (a) Calculated coupling efficiency for variation in a) adia-<br>batic III-V taper width, (b) n-InP thickness, (c) QW width<br>and (d) BCB thickness.                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 42 |

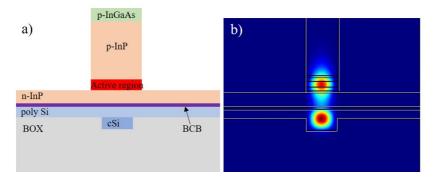

| 2.13 | Schematic illustration and simulated mode profile of the ISIPP50G waveguide crossection with integerated SOA.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 43 |

| 2.14 | Calculated $\gamma$ (left) and $\kappa$ map (right) to design the adiabatic taper for the ISIPP50G platform. The white dashed lines represent the selected III-V and Si width combinations for                                                                                                                                                                                                                                                                                                                                                                                                        |    |

|      | the full-coupling and partial-coupling designs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 43 |

| 2.15 | (left) Designed shape of the adiabatic alignment tolerant ta-<br>pers. The full-coupling design and partial-coupling design<br>is represented by the solid curves and the dashed curves,<br>respectively.                                                                                 | 44 |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

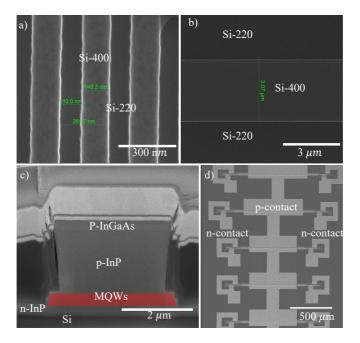

| 3.1  | Schematics and FIB cross-sections illustrating the design of the full-coupling and partial-coupling III-V-on-Si SOAs.                                                                                                                                                                     | 52 |

| 3.2  | Schematic of a complete photomask for SOA processing on an InP die                                                                                                                                                                                                                        | 54 |

| 3.3  | Schematic of different layers for SOA processing on InP.                                                                                                                                                                                                                                  | 54 |

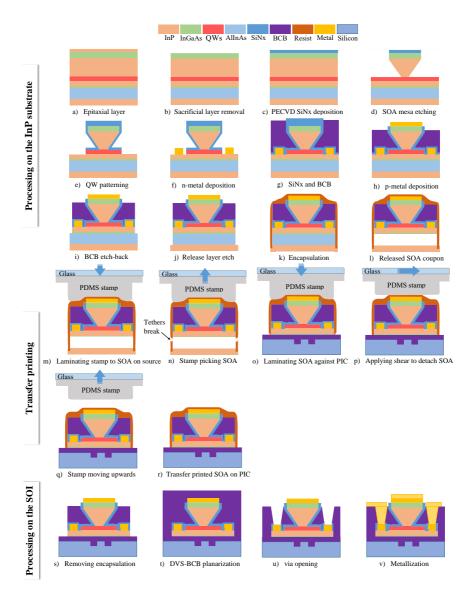

| 3.4  | The complete process flow of SOA device fabrication which includes patterning on the source InP substrate, micro-transfer-<br>printing, and final processing steps on the SOI target sub-<br>strate.                                                                                      | 55 |

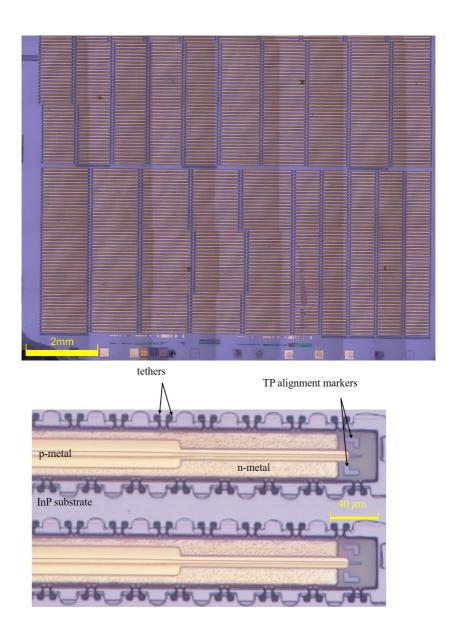

| 3.5  | (top) Microscope top image of an array of SOA devices<br>patterned and released on the native InP substrate, (bottom)<br>Zoomed-in microscope image of two SOA coupons                                                                                                                    | 57 |

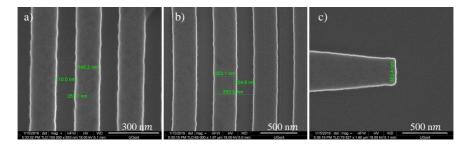

| 3.6  | a) SEM image of the DBR, b) grating coupler and c) taper<br>tip of the adiabatic taper in Si                                                                                                                                                                                              | 60 |

| 3.7  | Microscope image of a SOA coupon after micro-transfer-                                                                                                                                                                                                                                    |    |

| 2.0  | printing on SOI.                                                                                                                                                                                                                                                                          | 61 |

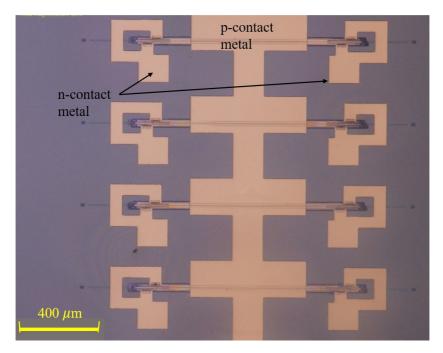

| 3.8  | Microscope image after contact metal deposition on the SOI.                                                                                                                                                                                                                               | 62 |

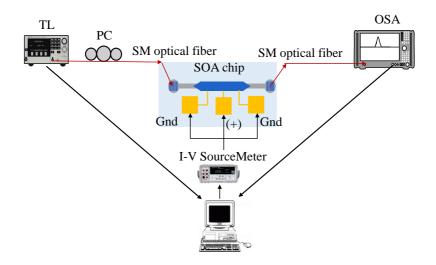

| 3.9  | The measurement setup used to characterize the SOAs, which<br>includes a tunable laser (TL), polarization controller (PC),<br>optical spectrum analyzer (OSA), and current-voltage source-<br>meter. The computer is used to control the instruments and<br>to process the measured data. | 63 |

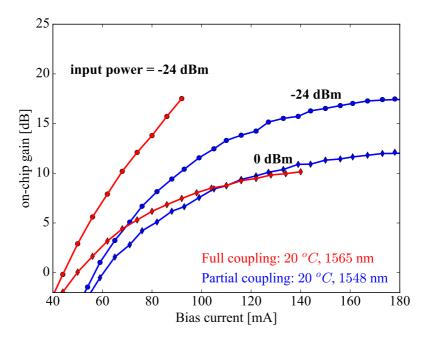

| 3.10 | The variation of on-chip gain with the bias current at lower<br>on-chip input power of $-24$ dBm and higher on-chip in-<br>put power of 0 dBm for both the full-coupling (in red) and                                                                                                     |    |

|      | partial-coupling (in blue) SOA design.                                                                                                                                                                                                                                                    | 65 |

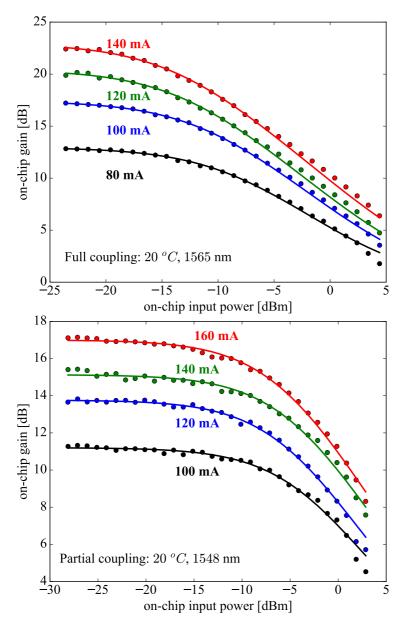

| 3.11 | Variation of the on-chip gain with the on-chip input power<br>for various bias currents, (top) for the full-coupling de-<br>sign at 1565 nm, (bottom) for the partial-coupling design<br>at 1548 nm. Data points represent the measured values and                                        |    |

|      | the solid lines are a fitting with Eq. $(3.1)$                                                                                                                                                                                                                                            | 66 |

| 3.12 | The markers represent the fitted values for $P_{\text{sat}}$ and for the small-signal gain $G_0$ for the full-coupling design (left) and                                                                                                                                                  |    |

|      | partial-coupling design (right).                                                                                                                                                                                                                                                          | 67 |

| 3.13 | On-chip gain measured as a function of wavelength and fit-<br>ted with Eq. (3.3) for (top) full-coupling SOA and (bottom)<br>SOA output spectrum measured with a 0 dBm input power<br>at 100 mA. The red and blue dotted lines indicates the ASE<br>level involved in the computation of the noise figure                                                                                                                                   | 68 |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

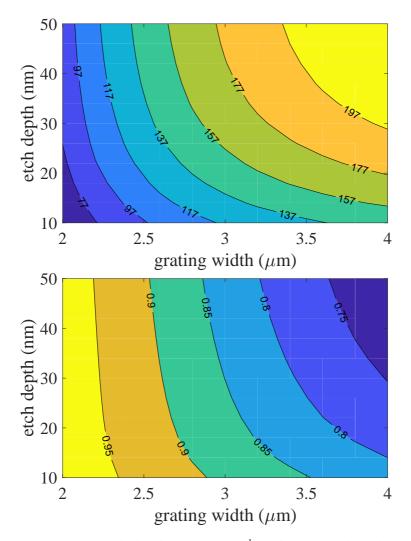

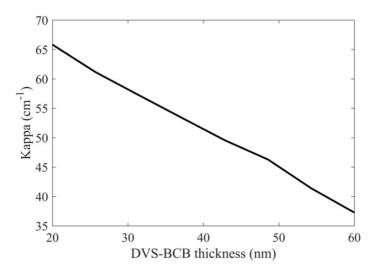

| 4.1  | (top) Calculated map of $\kappa$ in cm <sup>-1</sup> for different widths and<br>etch depths of the grating, (bottom) Calculated map of modal<br>overlap between etched and unetched section of the grating<br>for various grating widths and etch depths                                                                                                                                                                                   | 76 |

| 4.2  | Schematic illustrating the design of the DFB laser, the cross-<br>section view of the adiabatic taper and the side view of the<br>DFB grating.                                                                                                                                                                                                                                                                                              | 77 |

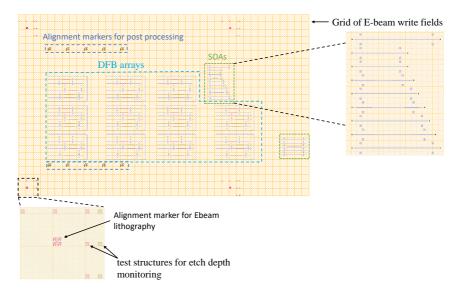

| 4.3  | Schematic illustrating the DFB SOI layout designed for processing with e-beam.                                                                                                                                                                                                                                                                                                                                                              | 77 |

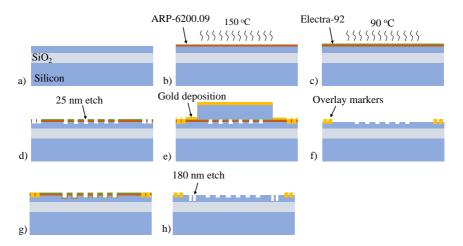

| 4.4  | a) 400 nm SOI wafer, b) Spin coating of ARP-6200.09 e-<br>beam resist and baking at 150 $^{o}$ C, c) Spin coating of charge<br>reduction layer Electra-92 at 90 $^{o}$ C, d) Development of the<br>e-beam resist and etching in RIE, e) Ti/Au deposition after<br>covering the chip with a Si piece, f) Lift-off and resist re-<br>moval, g) Repeat step (a-d), h) Final look at the SOI sample<br>with two etching steps.                  | 79 |

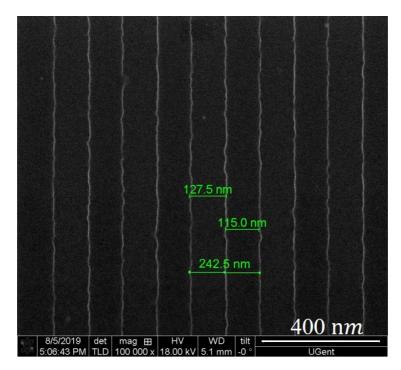

| 4.5  | SEM image of shallow etched grating                                                                                                                                                                                                                                                                                                                                                                                                         | 80 |

| 4.6  | Schematic micro-transfer-printing process flow of DFB lasers,<br>(a-d) depicts the processing of SOAs on the InP substrate,<br>(e) illustrates the preparation of the patterned SiPh sample<br>prior to micro-transfer-printing, (f-g) illustrates the picking<br>and printing of the SOAs on the SiPh sample, (h-i) illus-<br>trates the post-processing steps on the SiPh sample, which<br>includes passivation and electrical contacting | 82 |

| 4.7  | (a) Microscope image of SOA coupons micro-transfer printed<br>on SOI, (b) Zoomed-in image (c) after encapsulation re-<br>moval, (d) after Via opening for n-metal contact and (e)                                                                                                                                                                                                                                                           |    |

|      | final look after contact metal deposition                                                                                                                                                                                                                                                                                                                                                                                                   | 84 |

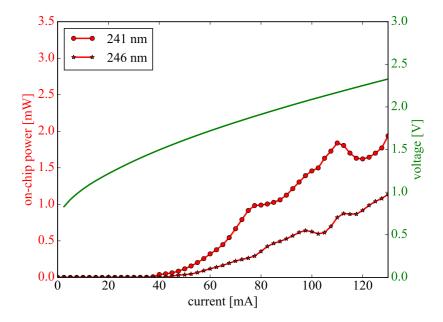

| 4.8  | Measured on-chip optical power and voltage versus bias current at 20 $^{\rm o}{\rm C}$ for a grating period of 241 nm and 246 nm.                                                                                                                                                                                                                                                                                                           | 85 |

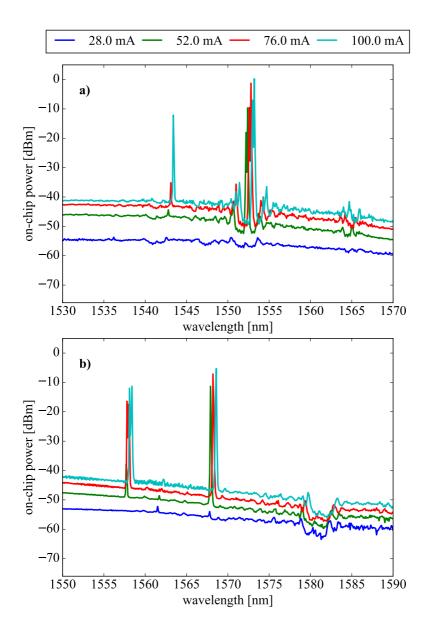

| 4.9  | Measured spectrum of shallow etch DFB lasers with grat-<br>ing period of (a) 241 nm and (b) 246 nm for various bias                                                                                                                                                                                                                                                                                                                         |    |

|      | currents                                                                                                                                                                                                                                                                                                                                                                                                                                    | 87 |

| ne DFB laser,<br>                                     |

|-------------------------------------------------------|

|                                                       |

| ser with cross-                                       |

|                                                       |

| e view of the                                         |

| on, b) longi-                                         |

| c) the mode                                           |

|                                                       |

| κ                                                     |

| deposition,                                           |

| r deposition,                                         |

| patterning of                                         |

|                                                       |

| e-sided) as a                                         |

|                                                       |

| temperatures                                          |

| n) Measured                                           |

| nd at 20 °C                                           |

|                                                       |

| (top) with chang-                                     |

| anging oper-                                          |

| 94                                                    |

| s currents at                                         |

| nperatures at                                         |

| Eset in the y-                                        |

| 95                                                    |

| tial-coupling                                         |

| ection is also                                        |

| 100                                                   |

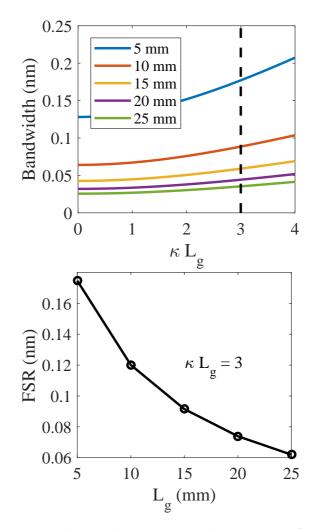

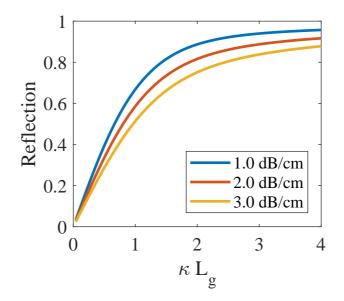

| against $\kappa L_q$                                  |

| - 0                                                   |

| SR of the FP                                          |

| ent lengths of                                        |

| 103                                                   |

| t the grating                                         |

| 104                                                   |

| ed-in images                                          |

| ction for the                                         |

| e laser in the                                        |

| d) Final look                                         |

| 105                                                   |

| detid . n N e l . d in a . sh . a n ff . r e n e h () |

| 5.5  | a) Image of the InP die after coupons have been picked for    |     |

|------|---------------------------------------------------------------|-----|

|      | micro-transfer printing, b) array of SOA coupons fabricated   |     |

|      | on the InP die, c) Micro-transfer printed SOA coupon on a     |     |

|      | Si waveguide and d) opening of n-vias for n-metal deposition. | 106 |

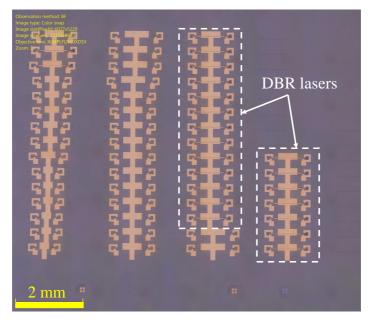

| 5.6  | Array of DBR lasers on the III-V-on-silicon die               | 107 |

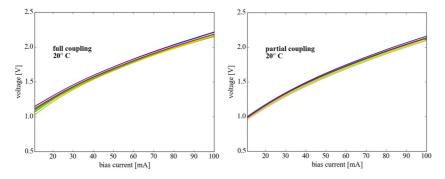

| 5.7  | Voltage versus bias current for (left) full-coupling design   |     |

|      | and (right) partial-coupling design.                          | 108 |

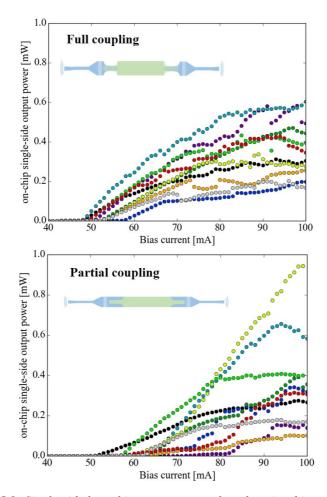

| 5.8  | Single-sided on-chip output power plotted against bias cur-   |     |

|      | rent for (top) full-coupling and (bottom) partial-coupling    |     |

|      | design                                                        | 109 |

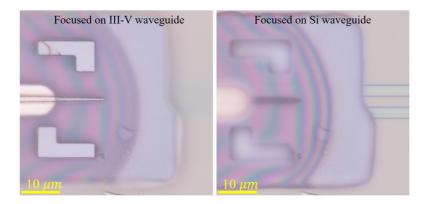

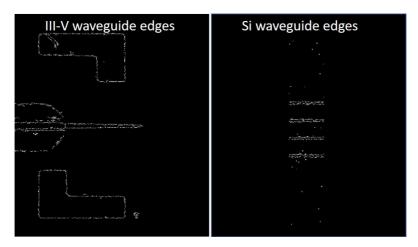

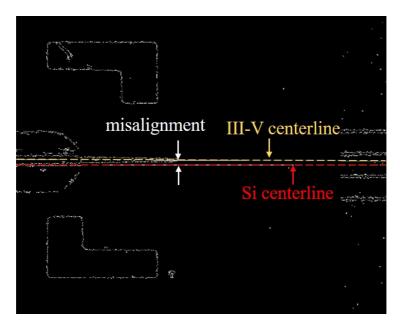

| 5.9  | 10x magnification microscope images of III-V and Si waveg-    |     |

|      | uide                                                          | 110 |

| 5.10 | III-V and Si waveguide image after edge detection             | 110 |

| 5.11 | III-V and Si waveguide image with center lines and mis-       |     |

|      | alignment labeled                                             | 111 |

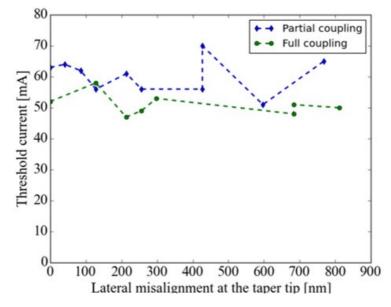

| 5.12 | DBR lasers threshold current plotted against the lateral mis- |     |

|      | alignment between III-V and Si waveguide                      | 112 |

| 5.13 | Process flow chart of misalignment measurement from the       |     |

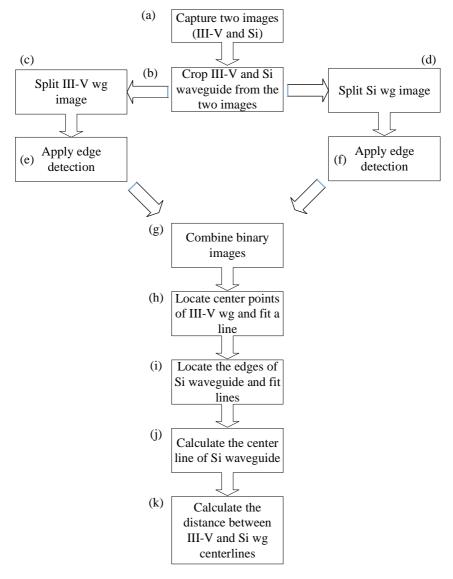

|      | microscope images of micro-transfer printed SOAs              | 113 |

# List of Tables

| 2.1 | III-V SOA epitaxial layer stack | 29 |

|-----|---------------------------------|----|

|-----|---------------------------------|----|

# List of Acronyms

| Α          |                                                     |

|------------|-----------------------------------------------------|

| AWG        | Arbitrary Waveform Generator                        |

| В          |                                                     |

| BOX<br>BW  | Buried Oxide<br>Bandwidth                           |

|            | Dandwiddi                                           |

| С          |                                                     |

| CW         | Continuous Wave                                     |

| CMOS       | Complementary metal oxide semiconductor             |

| D          |                                                     |

| DBR<br>DFB | Distributed Bragg Reflector<br>Distributed Feedback |

| DC         | Distributed Feedback<br>Direct Current              |

| DVS-BCB    | Divinylsiloxane-bis-Benzocyclobutene                |

### E

| EM  | Electromagnetism          |

|-----|---------------------------|

| EBL | Electron beam lithography |

| EME | Eigenmode Expansion       |

### F

| FOM  | Figure of merit               |

|------|-------------------------------|

| FEM  | Finite element method         |

| FWHM | Full width at half maximum    |

| FDTD | Finite-difference time-domain |

| FF   | Fill Factor                   |

| FSR  | Free Spectral Range           |

| FIB  | Focused Ion Beam              |

| FP   | Fabry-Perot                   |

H

| HC1   | Hydrochloric Acid |

|-------|-------------------|

| H3PO4 | Phosphoric acid   |

### I

| ICP | Inductively Coupled Plasma |

|-----|----------------------------|

|     |                            |

### L

LIDAR LI Light Detection And Ranging Light-Current

### Μ

| MZM<br>MQW | Mach Zehnder Modulator<br>Multiple Quantum Wells |

|------------|--------------------------------------------------|

| Ν          |                                                  |

| NRZ        | Non-Return-to-Zero                               |

| 0          |                                                  |

| OSA        | Optical Spectrum Analyzer                        |

| Р          |                                                  |

| PIC        | Photonic integrated circuit                      |

| PC         | Polarization Controller                          |

| PD         | Photodiode                                       |

| PDMS       | Polydimethylsiloxane                             |

| PECVD      | Plasma-Enhanced Chemical Vapor Deposition        |

| R          |                                                  |

| RIE        | Reactive Ion Etching                             |

| RF         | Radio Frequency                                  |

| Si<br>SiPh<br>SEM<br>SOI<br>SOA<br>SMSR | Silicon<br>Silicon Photonic<br>Scanning Electron Microscopy<br>Silicon-on-Insulator<br>Semiconductor Optical Amplifier<br>Side-Mode Suppression Ratio |

|-----------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|

| TE<br>TM<br>TL<br>TP                    | Transverse electric<br>Transverse magnetic<br>Tunable Laser<br>Transfer Printing                                                                      |

| W<br>WDM                                | Wavelength Division Multiplexing                                                                                                                      |

| Z                                       |                                                                                                                                                       |

| ZB                                      | Zettabytes                                                                                                                                            |

xxii

# Nederlandse samenvatting –Summary in Dutch–

In dit werk ontwikkelen we micro-transferprinttechnologie om III-V halfgeleider optische versterkers op siliciumgolfgeleidercircuits te integreren en deze te gebruiken om DFB-lasers en DBR-lasers te demonstreren.

Fotonica wordt beschouwd als één van de faciliterende technologieën van dit decennium. Fotonische geïntegreerde schakelingen worden in het bijzonder gebruikt om licht op micrometerschaal te genereren, te manipuleren en te detecteren. Eén van de vele toepassingen zijn optische interconnecties, die cruciaal zijn voor de toekomstige groei van de datacom-industrie. Optische verbindingen bestaan uit zenders en ontvangers voor snelle gegevensoverdracht in een datacenter, maar ook voor communicatie over langere afstanden. Andere snelgroeiende marktsegmenten zijn onder meer Li-DAR voor zelfrijdende auto's. In sommige implementaties maakt LiDAR gebruik van fotonische geïntegreerde schakelingen om miniatuurlichtbronnen en detectoren met laag vermogenverbruik te produceren tegen lage kost. Silicium fotonica is een veelbelovend integratieplatform voor goedkope en grootschalige fabricatie van de fotonische geïntegreerde schakeling. Inherent is het echter een bijna onmogelijke uitdaging om een efficiënte lichtbron in Si te produceren. Daarom worden andere materialen zoals III-Vhalfgeleiders op het SOI-substraat geïntegreerd.

Verschillende heterogene integeratietechnieken zijn in de loop der jaren ontwikkeld, waaronder directe en adhesieve hechting, monolithische integratie, hergroei op een hechtings-sjabloon en flip-chip-integratie. Sommige van deze technieken zijn technologisch meer volwassen dan de andere en allen hebben ze zowel voor- als nadelen. Micro-transferprinten is een nieuwe techniek voor de integratie van opto-elektronische componenten. Het biedt de voordelen van zowel flip-chip als adhesieve hechting, hetgeen betekent dat geteste componenten kunnen worden opgepikt met een stempel en in grote volumes kunnen worden geplaatst. Het principe

Figuur 1: Schematische voorstelling van het micro-transfer-printproces van geprefabriceerde SOA-coupons.

maakt gebruik van de visco-elastische eigenschap van de PDMS-stempels. De stempels kunnen, afhankelijk van hun kinetische energie, zich gedragen als een elastisch of visceus materiaal. Dit betekent dat wanneer een stempel na laminatie met de componenten met hoge snelheid wordt weggehaald, de componenten worden opgepikt door de PDMS-stempel. Aan de andere kant, wanneer de stempel met de componenten gelamineerd wordt met een ander substraat en de stempel traag verwijderd wordt, worden de componenten losgelaten door de stempel.

Figuur 1 toont het proces van micro-transferprinten van SOA-coupons (SOA: Semiconductor Optical Amplifier: Halfgeleider optische versterker). De III-V SOA is gedefinieerd op de InP-wafer. Dit proces omvat de vorming van SOA-mesa, het etsen van de actieve laag, contactmetaalafzetting, planarisatie met behulp van DVS-BCB en het terugetsen van het DVS-BCB en SiN-planarisatie om de coupons te realiseren. De opofferingslaag wordt vervolgens gestructureerd en coupons worden ingekapseld met een fotoresist. De opofferingslaag die in ons geval uit AlInAs bestaat, wordt ondergeëtst. Op dit punt worden de coupons zwak vastgehouden door fotoresiststructuren die aan het substraat zijn verankerd. De volgende stap is om het SOA-sample en het SOI-sample in de micro-transferprintto:ol te monteren. Deze tool maakt gebruik van beeldverwerking om de coupons uit te lijnen met het SOI substraat waarop geprint wordt. Uitlijningsmarkerin-

Figuur 2: Microscoopbeeld van a) verwerkte SOA-coupons op het InP-substraat,

b) twee SOA-coupons van (a) waarop wordt ingezoomd, c) geprinte SOA-coupon op een Si-golfgeleider, en d) III-V-on-Si SOA's met metaalcontacten.

gen hebben een patroon op zowel de III-V-coupons als op het SOI-substraat om elke coupon uit te lijnen met betrekking tot het Si-golfgeleidercircuit. Wanneer de installatie en uitlijning is voltooid, gaat de stempel naar de opgeslagen x-y-coördinaat op de bron, lamineert een coupon en pikt deze op. Vervolgens beweegt de stempel naar de opgeslagen x-y-coördinaat op het doel, delamineert de coupon en plaatst deze op de gewenste locatie. Nadat alle coupons zijn getransfereerd, wordt de inkapseling verwijderd en wordt de DVS-BCB lijmlaag volledig uitgehard. De laatste stap is het elektrisch contacteren van de component. Figuur 1 toont microscoopbeelden van de III-V-on-Si SOA's bij verschillende processtappen. De uitlijning van de III-V SOA met de Si-golfgeleider is een belangrijke parameter. De beste micro-transferprinttools kunnen een uitlijningstolerantie van  $(3 \sigma) \pm 1.5 \mu m$  bieden. Dit betekent dat III-V/Si adiabatische koppeling een goede koppelingsefficiëntie moet hebben binnen de genoemde uitlijningstolerantie. Dit is met name belangrijk voor de ontwikkeling van SOA's met hoge versterking. Daarom hebben we twee adiabatische koppelingsstructuren ontworpen met een uitlijningstolerantie van 1,0  $\mu$ m en 1,5  $\mu$ m als het slechtste geval voor volledige en gedeeltelijke koppeling tussen Si

Figuur 3: (links) De III-V en Si adiabatische koppelstructuur in de lengterichting. De blauwe lijn en de linker verticale as stellen de III-V adiabatische conische vorm voor de gedeeltelijke en volledige koppelingsontwerpen. De rode lijn en de rechter verticale as representeren de adiabatische conische vorm van Si en de breedte van de Si golfgeleider in het geval van respectievelijk volledige koppeling en gedeeltelijke koppeling; (rechts) De gesimuleerde koppelingsefficiëntie van de adiabatische structuren voor de ontwerpen voor gedeeltelijke en volledige koppeling versus de laterale uitlijning.

#### en III-V.

Figuur 3 illustreert de vorm van de twee ontworpe n adiabatische koppelingsstructuren en de efficiëntie van de koppeling tegen de laterale uitlijningsfout. De Si adiabatische structuur tapert van 0,2  $\mu$ m naar 3,2  $\mu$ m en het III-V tapert van 3,0  $\mu$ m naar 0,5  $\mu$ m. Bovendien is de berekende koppelingsefficiëntie voor zowel de structuren voor gedeeltelijke koppeling als voor de structuren voor volledige koppeling groter dan -0,3 dB voor een verkeerde uitlijning van  $\pm$  1,0  $\mu$ m.

De epitaxiale SOA-stack heeft een hooggedoteerde p-InGaAs-contactlaag met een dikte van 200 nm, een p-InP-bekleding met een dikte van 1,5  $\mu$ m di, een InGaAsP-etsstoplaag van 25 nm, een paar AlGaInAs lagen van 40 nm, overgangslagen die InP van SCH-lagen scheiden, een paar 75 nm AlGaInAs SCH-lagen, een actief gebied met 6 AlGaInAs QW's ingeklemd tussen AlGaInAs-barrièrelagen, een 200 nm n-InP-contactlaag met 60 nm intrinsieke InP-laag eronder en een 50 nm/500 nm InGaAs/AlInAs-opofferingslaag gegroeid op het InP-substraat.

We hebben twee III-V-op-Si SOA-ontwerpen ontwikkeld die een verschillende Si-golfgeleiderbreedte hebben in het versterkingsgedeelte van de SOA. Dit maakt het mogelijk om de opsluiting van de optische modes in de kwantumputten te variëren en zo de klein-signaalversterking en het uitgangsverzadigingsvermogen af te stemmen. De Si-golfgeleiderlaag is 400 nm dik en heeft een etsdiepte van 180 nm. De begraven oxidelaag

Figuur 4: Schema's en FIB-doorsneden die het ontwerp van de volledige koppeling en gedeeltelijke koppeling voor III-V-op-Si SOA's illustreren.

(BOX) is 2  $\mu$ m dik onder de Si-golfgeleiderlaag. Beide SOA-ontwerpen, volledige koppeling (hogere optische opsluiting in de QW's) en gedeeltelijke koppeling (lagere optische opsluiting in de QW's), worden geïllustreerd in figuur 4. De III-V-op-Si SOA wordt voor de metingen op een houder geplaatst waarvan de temperatuur constant gehouden wordt op 20 °C. De versterker wordt optisch uitgelezen met single-mode vezels. Roosterkoppelaars worden gebruikt om het licht te koppelen naar de optische vezels. De roosterkoppelaars hebben een golflengte-afhankelijke transmissie. Daarom is het nodig om roosterkoppelaars te karakteriseren als een functie van de golflengte om de versterking op de chip nauwkeurig te kunnen meten. Om dit te doen, worden referentie Si-golfgeleiders op dezelfde chip als de versterkers gerealiseerd en ondergaan ze dezelfde processtappen als de roosterkoppelaars die worden gebruikt om de SOA's te analyseren. De golflengteafhankelijke transmissie van de roosterkoppelaars wordt gemeten met behulp van een afstembare laser (Santec TSL-510) en een optische spectrumanalysator (OSA, Advantest Q8381A). De hoek van de vezelhouders is geoptimaliseerd om de maximale transmissiegolflengte van de roosterkoppelaars uit te lijnen met de versterkingspiek van de twee besproken SOA's. Aangezien de III-V SOA's die op beide SOI-ontwerpen zijn geprint nominaal hetzelfde zijn, is de serieweerstand ook nominaal hetzelfde,  $10, 0 \Omega$ bij een stroom van 80 mA stroom of een stroomdichtheid van 1,8 kA/cm<sup>2</sup>.

Figuur 5: Variatie van de versterking op de chip met het ingangsvermogen op de chip voor verschillende instelstromen, (links) voor het ontwerp met volledige koppeling bij 1565 nm, (rechts) voor het ontwerp met de gedeeltelijke koppeling bij 1548 nm.

Figuur 5 illustreert de gemeten versterking op chip van de SOA's voor verschillende stromen. Het maximale uitgangsvermogen is 10,8 dBm voor een golflengte van 1565 nm (bij 140 mA) en 11, 3 dBm voor een golflengte van 1548 nm (bij 160 mA) voor respectievelijk volledige koppeling en gedeeltelijke koppeling.  $P_{sat}$  is 12,8 mW en 9,0 mW voor respectievelijk de gedeeltelijke en volledige koppeling. De SOA met gedeeltelijke koppeling (en lagere overlap met de actieve laag) heeft een maximum  $P_{sat}$  van 15 mW bij 160 mA instelstroom (417 mW vermogensdissipatie) en een kleinsignaalversterking van 17 dB. Ter vergelijking: de SOA met volledige koppeling (en hogere overlap met de actieve laag) heeft een maximum  $P_{sat}$ van 9,2 mW bij 140 mA instelstroom (336 mW vermogensdissipatie) en een kleinsignaalversterking van 23 dB. De SOA met een hogere overlap leidt dus tot meer versterking, maar heeft een lager verzadigingsvermogen en vice versa. De 3dB-versterkingsbandbreedte van de SOA neemt toe met de biasstroom en is 30 nm bij 120 mA (2,71 kA/cm<sup>2</sup>). Een vergelijkbare versterkingsbandbreedte wordt verkregen voor de structuur met gedeeltelijke koppeling. Voor 100 mA stroom en een golflengte van 1565 nm is het ruisgetal  $F_{siq-ASE} \approx 8,6$  dB voor een ingangsvermogen op de chip van -24 dBm en is  $F_{sig-ASE} \approx 9,54$  dB bij 0 dBm ingangsvermogen. Evenzo heeft bij 1548 nm de SOA met gedeeltelijke koppeling een ruisgetal  $F_{sig-ASE} \approx 7,0$  dB bij -24 dBm on-chip ingangsvermogen en  $F_{siq-ASE} \approx 8,6$  dB bij 0 dBm ingangsvermogen op de chip. De SOA's laten prestaties zien die vergelijkbaar zijn met de componenten die zijn gemaakt met andere heterogene integratietechnologieën.

In de volgende stap hebben we III-V-op-silicium DFB-lasers ontwik-

Figuur 6: Schematische voorstelling van het ontwerp van de DFB-laser met aanzicht in dwarsdoorsnede van de adiabatische structuur en het zijaanzicht van het DFB-rooster. SEM-afbeeldingen van a) overgang tussen DFB sectie en passieve siliciumgolfgeleider, b) longitudinale dwarsdoorsnede van het DFB-rooster en c) het modeprofiel in de versterkingssectie.

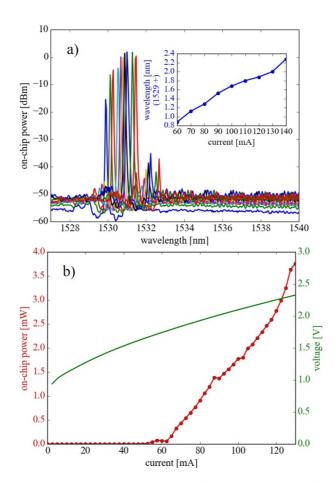

keld door de SOA's te integreren op een eerste orde diffractierooster. Het siliciumgolfgeleiderplatform bestaat uit een 400 nm dikke Si-golfgeleiderlaag op een 2  $\mu$ m dikke oxide laag (BOX). De Si-golfgeleider in het versterkingsgedeelte van de DFB-laser is 2,0  $\mu$ m breed en heeft een etsdiepte van 20 nm. De golfgeleider wordt gedefinieerd door het etsen van 3,0  $\mu$ m brede sleuven. 50 nm PECVD SiN wordt afgezet en periodiek geëtst op de bovenkant van de Si-golfgeleider om het diffractieroorster te definiëren. Het ontwerpschema en de longitudinale doorsnede worden geïllustreerd in Fig. 6. De serieweerstand van de laser is 8,0  $\Omega$ . Figuur 7(links) toont de LI-curve voor de DFB-laser bij verschillende bedrijfstemperaturen. Een enkelzijdig golfgeleidergekoppeld optisch vermogen van 9,1 mW, 6,9 mW en 2,8 mW wordt verkregen bij 15 °C, 20 °C en 25 °C, respectievelijk. De drempelstroom bij 20 °C is 80 mA en neemt toe met de stijging van de bedrijfstemperatuur. De differentielë efficientie is 0,27 W/A bij 20 °C. Monomodale

Figuur 7: (boven) Golfgeleider-gekoppeld uitgangsvermogen (enkel-zijdig) als functie van stroom voor verschillende bedrijfstemperaturen en de stroom-spanningskarakteristiek, (onder) Gemeten spectrum (0,05 nm resolutie) bij 90 mA en 20 °C bedrijfstemperatuur.

werking bij een golflengte van 1558,3 nm met een onderdrukking van de zijmode van meer dan 33 dB wordt verkregen bij 90 mA, zoals te zien in Fig. 7(rechts). De DFB stopband is 2 nm breed, wat overeenkomt met een  $\kappa$  L van 2,6.

Bovendien demonstreerden we ook DBR-lasers met behulp van de ontwikkelde technologie en onderzochten we het effect van het micro-transferprinten op de prestaties van de laser, met name de drempelstroom. Microtransfer-printing kan extra verlies in de lasercaviteit veroorzaken en daardoor de drempelstroom verhogen. We vonden echter geen verband tussen de drempelstroom en de verkeerde uitlijning tussen de III-V en Sigolfgeleider.

# **English Summary**

In this work, we develop micro-transfer-printing technology for integrating processed SOA devices on silicon waveguide circuits and use them to demonstrate DFB and DBR lasers.

Photonics has been recently coined as one of the disruptive technologies of the next decade. Photonic integrated circuits are in particular used to generate, manipulate and detect light on the micron scale. One of the several applications include optical interconnects that are crucial for the prospective growth of the datacom industry. Optical interconnects consist of transmitters and receivers for high speed data transfer in a data center. Other rapidly growing market segment is LiDAR. In some implementations, LiDAR relies on photonic integrated circuits to produce miniature low-cost sources and detectors. Silicon photonics is a promising platform for low-cost and high volume manufacturing of the photonic integrated circuits. Inherently, it is challenging to produce efficient and high-performance light sources in Si. Therefore, other materials such as III-V semiconductors need to be integrated on the SOI substrate.

Several heterogeneous integration techniques have been developed over the years: direct and adhesive bonding, monolithic integration, regrowth on a bonding template and flip-chip integration. Some of these techniques are technologically more mature than the others and they all have their own pros and cons. Micro-transfer printing is a novel technique for the integration of opto-electronic devices. It offers the combined benefits of flip-chip and adhesive bonding, which means that pre-processed and tested devices can be picked and placed massively parallel. The technique takes advantage of the viscoelastic properties of the PDMS stamp used to pick up and print devices. The stamps, depending on their kinetic energy, can behave either as an elastic or viscous material. This simply means that when stamps that are laminated with the devices are removed with high velocity, the devices get attached to the PDMS stamp. On the other hand, when the stamp is slowly removed after printing the coupons on the target wafer and a shear

Figure 8: Schematic illustrating the micro-transfer printing process of pre-processed SOA coupons.

force is applied, the devices get detached from the stamp. Hence, dependent on the size of the stamp and the number of posts, multiple devices can be transferred from the source substrate to the target substrate.

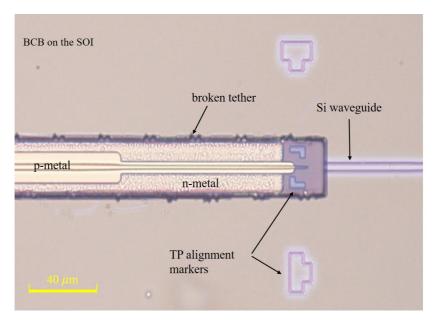

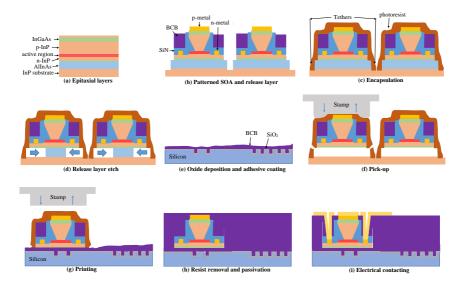

Figure 8 depicts the process flow for the micro-transfer printing of patterned SOA coupons. The III-V SOA is patterned on the InP wafer. This patterning involves the formation of the SOA mesa, patterning of the QWs, contact-metal deposition, planarization using DVS-BCB and etch-back of the DVS-BCB and SiN and patterning of the coupon boundary. The sacrificial layer is then patterned and coupons are encapsulated with a photoresist. The sacrificial layer which is AlInAs in our case is under-etched. At this point, the coupons are held in place by tethers anchored to the substrate. The next step is to mount the released III-V SOA sample and the SOI sample on their respective translation stage in the micro-transfer printing tool. This tool uses image processing to align the source and target coupons in the x-y plane. Alignment markers are patterned on both the III-V coupons and on the SOI target to align each coupon with respect to the Si waveguide circuit in the x-y plane. After all the coupons have been printed, the encapsulation from the printed coupons is removed and the DVS-BCB adhesive layer is fully cured to strongly bind the coupons at the printed location. The final processing step is to deposit metal pads to probe the device. Figure 9 shows microscope images of the III-V-on-Si SOAs at various processing

Figure 9: Microscope image of a) processed SOA coupons on the InP substrate, b) two zoomed-in SOA coupons from (a), c) micro-transfer-printed SOA coupon on a Si waveguide, and d) III-V-on-Si SOAs with contact pads.

steps.

The alignment of the III-V SOA with the Si waveguide is an important parameter. The state-of-the-art micro-transfer printing tools can provide an alignment tolerance of  $\pm 1.5 \ \mu m (3\sigma)$ . This means that the evanescent III-V/Si adiabatic taper must have good coupling efficiency within the aforementioned alignment tolerance. This is particularly important for the development of high gain SOAs. Therefore, we designed two adiabatic tapers taking 1.0  $\mu m$  alignment tolerance and 1.5  $\mu m$  as the worst case for full coupling and partial coupling into the III-V SOA. The partial-coupling III-V adiabatic taper is design for coupling design the III-V and Si are both inversely tapered. Figure 10 illustrates the shape of the two adiabatic taper designs and coupling efficiency against the lateral misalignment. The calculated coupling efficiency for both the partial-coupling and full-coupling designs are greater than -0.3 dB for 1.0  $\mu m$  misalignment. In the partial-coupling design a 1.5  $\mu m$  misalignment leads to 1dB excess loss.

The SOA epitaxial stack has a 200 nm highly doped p-InGaAs contact layer, a 1.5  $\mu$ m p-InP cladding, a 25 nm InGaAsP etch stop layer, a pair

Figure 10: (left) The III-V and Si adiabatic taper width variation along its length. The blue line and the left vertical axis represents the III-V adiabatic taper shape for the partial and full coupling designs. The red line and the right vertical axis represents the Si adiabatic taper shape and Si waveguide width in the case of full coupling and partial coupling, respectively; (right) The simulated coupling efficiency of the adiabatic taper structures for the partial and full-coupling designs versus the lateral misalignment.

of 40 nm AlGaInAs transition layers separating InP from SCH layers, a pair of 75 nm AlGaInAs SCH layers, an active region with 6 AlGaInAs QWs sandwiched between AlGaInAs barrier layers, a 200 nm n-InP contact layer with 60 nm intrinsic InP layer underneath and a 50 nm/500 nm InGaAs/AlInAs release layer grown on the InP substrate.

We developed two III-V-on-Si SOA designs that either have or do not have a Si waveguide underneath the gain section of the SOA. This allows to vary the confinement of the optical mode in the quantum wells and hence tune the small-signal gain and output saturation power. The Si waveguide layer is 400 nm thick and has a 180 nm etch depth. The buried oxide (BOX) layer is 2  $\mu$ m thick underneath the Si waveguide layer. Both SOA designs, full coupling (higher optical confinement in the QWs) and partial coupling (lower optical confinement in the QWs), are illustrated in Fig. 11. The III-V-on-Si SOA is placed on a temperature-controlled stage at 20 °C for the measurements. The PIC is optically probed with cleaved standard single mode fibers using a fiber stage. Grating couplers are used to interface with the optical fibers. The grating couplers that couple light into the PIC have a wavelength-dependent transmission. Therefore, it is necessary to characterize the grating coupler efficiency as a function of wavelength to measure the on-chip gain of the amplifiers accurately. In order to do this, reference passive Si waveguides are also fabricated along with amplifiers on the same chip and they undergo the same processing steps as the grating couplers used for interfacing with the SOAs. The wavelength-dependent

Figure 11: Schematics and FIB cross-sections illustrating the design of the full-coupling and partial-coupling III-V-on-Si SOAs.

Figure 12: Variation of the on-chip gain with the on-chip input power for various bias currents, (left) for the full-coupling design at 1565 nm, (right) for the partial-coupling design at 1548 nm.