(19)

(12)

Europäisches Patentamt European Patent Office Office européen des brevets

# (11) **EP 3 038 167 A1**

EUROPEAN PATENT APPLICATION

## (54) Integrated avalanche germanium photodetector

(57) An integrated avalanche photodetector and a method for fabrication thereof. The integrated avalanche photodetector 100 comprises a Ge body 110 adapted to conduct and optical mode. The Ge body 110 comprises a first p-doped region 120, for the absorption of an optical mode. The first p-doped region 120 extends from a first main surface 111 to a second main surface 112 of the Ge body 110. The Ge body 110 comprises a first n-doped region 130 that extends from the first main surface 111 to wards the second main surface 112 of the Ge body

110. An intrinsic region 115 occupies the undoped part of the Ge body 110. A first avalanche junction is formed by the first n-doped region 130 that is located aside the p-doped region 120. The Ge body 110 comprises an incidence surface 310, suitable for receiving an optical mode 300. The incidence surface 310 is perpendicular to the first avalanche junction. A second n-doped Ge region 140 that covers the Ge body 110 and forms a second PN avalanche junction with the first p-doped region 120 at the first main surface 111.

Printed by Jouve, 75001 PARIS (FR)

#### Description

#### **Technical field**

**[0001]** The present disclosure is related to an integrated avalanche germanium photodetector.

**[0002]** The present disclosure also relates to a use of the integrated avalanche photodetector and to a method for fabrication thereof.

#### State of the art

**[0003]** The field of planar integrated optical photodetector for telecommunication in the near IR band has been using germanium (Ge) as absorption layer thanks to the large absorption coefficient of Ge at the near IR wavelengths. Si is transparent at these IR wavelength and cannot be used as a photodetector.

**[0004]** Paper "Germanium avalanche receiver for low power interconnects" Nature Communications 5, Article number:4957, by Leopold Virot further referred to as Virot paper, discloses a waveguide avalanche Ge photodiode, capable of detection at 10Gbit per second under low bias conditions. A lateral Ge PIN diode is described that has a thin (500nm) Ge multiplication region and a Ge absorption region. Efficient butt-coupling was demonstrated by directly connecting the Si waveguide to the Ge absorption region. The dark current increases to 610uA at -7V bias in avalanche conditions. The quality of the Ge crystal grown was verified by a low value of the dark current at low bias conditions, i.e. 18nA at -1V bias.

**[0005]** The paper "Silicon Optical Interconnect Device Technologies for 40Gb/s and beyond" IEEE journal of selected topics in quantum electronics VOL. 19, NO.2 MARCH/APRIL 2013 by Tsung-Yang Liow, further referred to as Liow paper, discloses that a lateral Ge PIN avalanche detector has a significant increase in dark current after being stressed for 15 minutes at a reverse bias of -9V, compared to pristine unstressed device. The cause is believed to be related to mid-bandgap states which could be located at the Ge to cladding oxide interface. Some partial recovery was also observed.

**[0006]** There is a need to limit the increase in dark current, due to the application of an initial high reverse bias voltage for an avalanche photodiode.

#### Summary

**[0007]** The present disclosure aims to reduce, the increase in the dark current after initial voltage stress of an integrated germanium (Ge) photodetector. It thus is an advantage of embodiments of the present invention that the dark current increase in integrated Ge photodetectors, as for example observed in the Liow paper, can be reduced. This is achieved with an integrated avalanche detector according to the characterizing part of the first claim, or by the use of such an integrated avalanche detector for detecting radiation.

**[0008]** In a first aspect, the integrated avalanche photodetector comprises a Ge body adapted to conduct an optical mode. The Ge body comprises a first p-doped region, for absorption of the optical mode, extending from a first main surface to a second main surface of the Ge body. The Ge body also comprises a first n-doped region aside the first p-doped region, and extends from the first main surface towards the second main surface of the Ge body, and forms a first avalanche junction with the first

<sup>10</sup> p-doped region. The Ge body also comprises an intrinsic region that occupies the undoped part of the Ge body. The Ge body has an incidence surface, suitable for receiving the optical mode, perpendicular to the first avalanche junction. According to the first aspect, the inte-

<sup>15</sup> grated avalanche photodetector comprises a second ndoped Ge region, that covers the Ge body and forms a second PN avalanche junction with the first p-doped region at the first main surface. It has been found that the latter reduces the increase in dark current of the integrat-

<sup>20</sup> ed avalanche photodetector compared to for example the Ge avalanche photodetector according to the prior art as described above.

[0009] According to some embodiments, the second PN avalanche junction, when in use, has a depletion zone

that is spaced at least 20nm from an upper main surface of the second n-doped Ge region. It has been found that spacing the mid-bandgap states, located at the upper main surface, from the depletion zone, prevents these mid-bandgap states at the upper main surface to undergo

the high electric fields, needed for avalanche multiplica-

tion, and thus prevents those mid-bandgap states to contribute to the dark current under avalanche conditions.

[0010] According to some embodiments the second n-doped Ge region has the upper main surface perpendicular to the incidence surface. Such incidence surface can be used in a butt-coupling configuration, so that the optical mode can propagate into the absorption region in a direction parallel with the second n-doped Ge region.

[0011] According to some embodiments the second ndoped Ge region is connected to a cathode electrode from the upper main surface of the second n-doped Ge region, and the first p-doped region is connected to an anode electrode through a second p-doped semiconductor region, which is in direct contact with the first p-doped

<sup>45</sup> region at the second main surface. Such anode and cathode electrodes can be used to connect the photodetector in an electrical circuit.

[0012] According to some embodiments, the first p-doped region is not in contact with a sidewall of the Ge

<sup>50</sup> body perpendicular to the incidence surface, which has been found to further improve the dark current at avalanche conditions, as the high electric field is spaced from the mid-bandgap states of the Ge body at a sidewall.

[0013] According to some embodiments the first ndoped region is in direct contact with the first p-doped region and the first avalanche junction is a PN avalanche junction, which has been found to further lower the reverse bias voltage needed for avalanche conditions. **[0014]** According to some embodiments, the integrated avalanche photodetector, wherein the first n-doped region is spaced from the first p-doped region and the first avalanche junction is a PIN avalanche junction, has been found to achieve a dark current reduction over the prior art.

**[0015]** According to some embodiments, the first ndoped region is fully extending through the Ge body and is connected to the cathode electrode through a third ndoped semiconductor region, which is in direct contact with the first n-doped region at the second main surface, and the first p-doped region is connected to the anode electrode through the second p-doped semiconductor region, which is in direct contact with the first p-doped region at the second main surface, thus providing an alternative electrical connection to an electrical circuit compatible with a planar integration technology.

**[0016]** According to some embodiments, the integrated avalanche photodetector further comprises a planar integrated semiconductor waveguide configured to couple the optical mode to the Ge body through the incidence surface, thereby forming an integrated waveguide avalanche photodetector that can be used in planar integration technologies.

**[0017]** According to some embodiments, the integrated avalanche photodetector, further comprising a taper adapted to conduct the optical mode from the integrated semiconductor waveguide to the incidence surface, has been found to increase the coupling of an optical mode into the Ge body.

**[0018]** According to some embodiments the integrated avalanche photodetector, wherein the second p-doped semiconductor region, the third n-doped semiconductor region and the integrated semiconductor waveguide are formed in a single planar semiconductor layer, has been found to be easily integrated in readily available planar semiconductor on insulator (SOI) substrates.

**[0019]** According to some embodiments the planar semiconductor layer is silicon and the Ge body is covered with Silicon oxide.

**[0020]** In a second aspect the present disclosure relates to the use of a photodetector for detecting radiation according to the first aspect, whereby such a photodetector, when in use at reverse bias conditions for avalanche multiplication, has a reduced dark current compared to for example the Ge avalanche photodetector according to prior art, as described above.

**[0021]** According to some embodiments, a reverse bias is applied to the first avalanche junction and the second avalanche junction. It has been found that when the reverse bias is increased to achieve avalanche multiplication in the first and second avalanche junctions, there is a reduction of the dark current compared to the prior art, as the mid-bandgap states at the upper main surface are spaced from the first avalanche junction and the second avalanche junction by the second n-doped Ge region, this prevents the mid-bandgap states at the upper main surface to undergo the high electric fields, needed for avalanche multiplication in the first avalanche junction and the second avalanche junction, and thus prevents those the mid-bandgap states contribute to the increase of the dark current under avalanche conditions.

<sup>5</sup> **[0022]** A third aspect of the present disclosure relates to a method for fabricating an integrated avalanche photo detector according to the first aspect, the method comprising: providing an intrinsic Ge body adapted to conduct an optical mode; and doping a region, extending from a

<sup>10</sup> first main surface to a second main surface of the Ge body, with a p-type dopant to obtain a first p-doped region; and doping a region extending from the first main surface towards the second main surface of the Ge body, with a n-type dopant to obtain a first n-doped region; and

<sup>15</sup> forming a first avalanche junction with the first n-doped region located aside the first p-doped region; and providing an incidence surface on the Ge body suitable for optical mode incidence, perpendicular to the first avalanche junction; and providing a second n-doped Ge region that

<sup>20</sup> covers the Ge body to form a second PN avalanche junction with the first p-doped region at the first main surface.

[0023] The method for fabricating an integrated avalanche photo detector, wherein providing the Ge body comprises: providing a semiconductor layer; and forming

a second p-doped semiconductor region in the semiconductor layer, in the location where the first p-doped region will be formed; and optionally forming a third n-doped semiconductor region in the semiconductor layer, in the location where the first n-doped region will be formed;

and after doping the semiconductor layer, providing the Ge body on top of and in contact with the semiconductor layer at the second main surface.

#### Brief description of the figures

#### [0024]

35

40

45

50

55

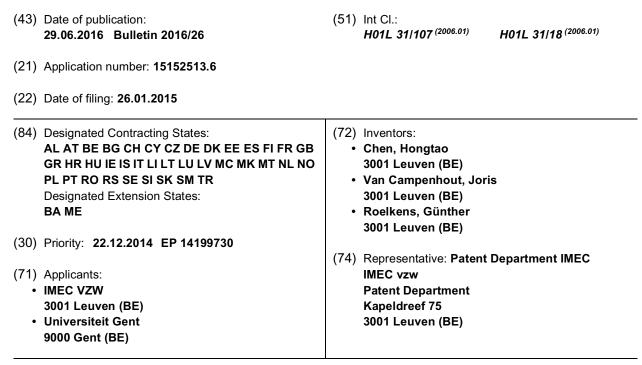

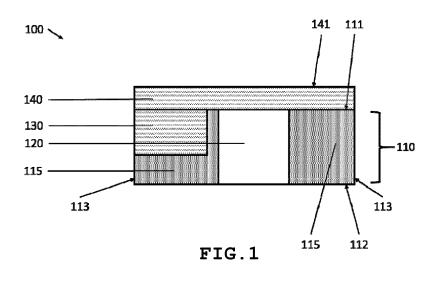

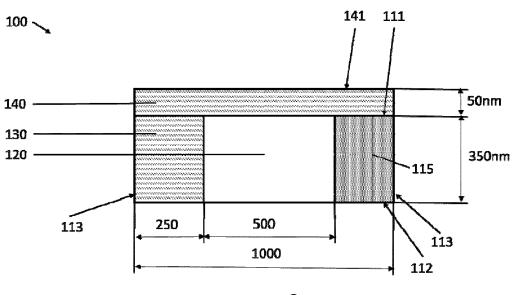

FIG 1 illustrates a cross section of the integrated avalanche photodetector according to embodiments of the present disclosure.

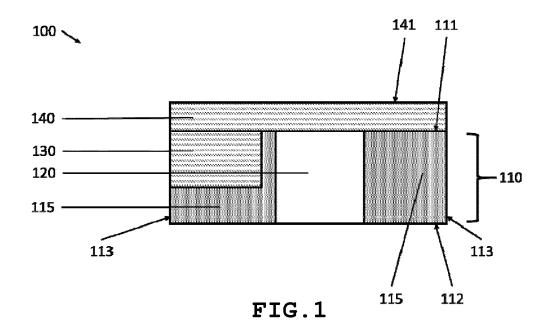

FIG 2 illustrates a three dimensional view of the integrated avalanche photodetector according to embodiments of the present disclosure.

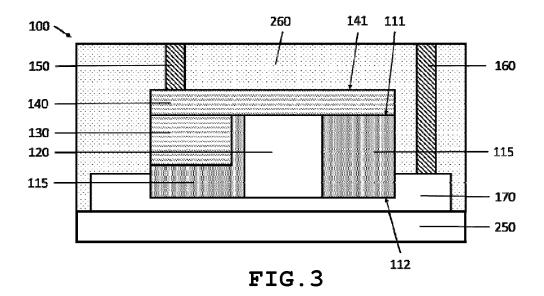

FIG 3 illustrate a cross section of the integrated avalanche photodetector according to embodiments of the present disclosure.

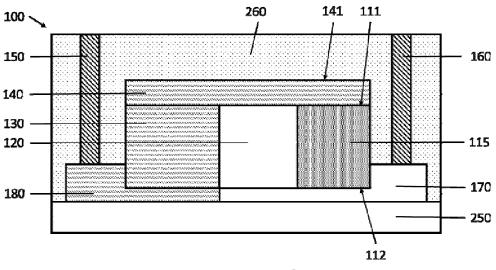

FIG 4 illustrate a cross section of the integrated avalanche photodetector according to embodiments of the present disclosure.

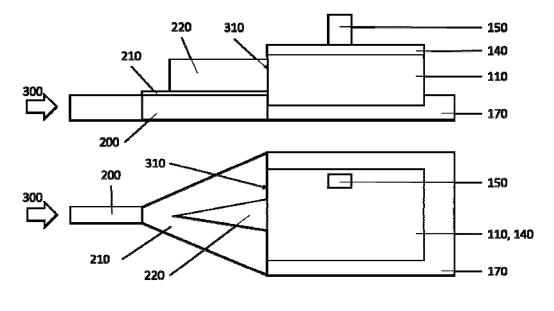

FIG 5 illustrates a top and side view of an integrated waveguide avalanche photodetector according to embodiments of the present disclosure.

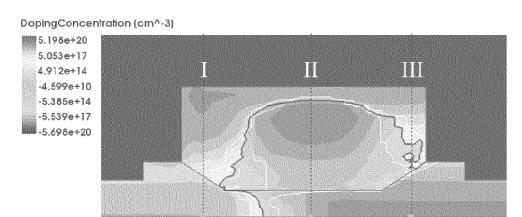

FIG 6 illustrates doping concentrations according to an exemplary embodiment of the present disclosure.

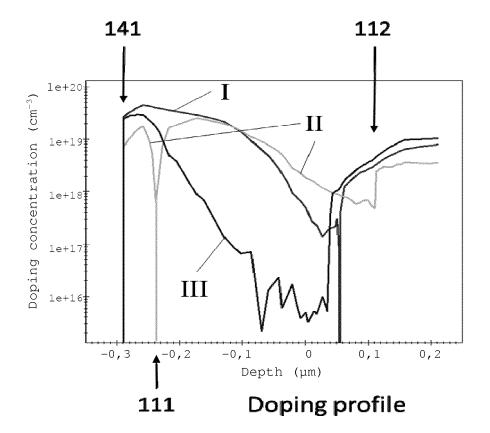

FIG 7 illustrates doping profiles in a number of cross sections according to an exemplary embodiment of the present disclosure.

FIG 8 illustrates an exemplary integrated avalanche

30

35

photodetector according to an embodiment of the present disclosure.

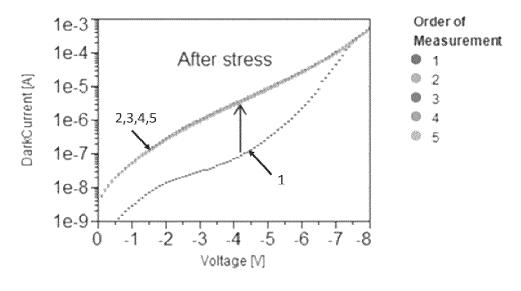

FIG 9 illustrates measurements, of an examplary Ge photodetector according to the prior art, before and after reverse bias voltage stress.

#### **Detailed description**

**[0025]** The present disclosure will be described with respect to particular embodiments and with reference to certain drawings but the disclosure is not limited thereto. The drawings described are only schematic and are non-limiting. In the drawings, the size of some of the elements may be exaggerated and not drawn on scale for illustrative purposes. The dimensions and the relative dimensions do not correspond to actual reductions to practice of the disclosure.

**[0026]** Furthermore, the terms first, second and the like in the description, are used for distinguishing between similar elements and not necessarily for describing a sequence, either temporally, spatially, in ranking or in any other manner. It is to be understood that the terms so used are interchangeable under appropriate circumstances and that the embodiments of the disclosure described herein are capable of operation in other sequences than described or illustrated herein.

**[0027]** Moreover, the terms top, under and the like in the description are used for descriptive purposes and not necessarily for describing relative positions. It is to be understood that the terms so used are interchangeable under appropriate circumstances and that the embodiments of the disclosure described herein are capable of operation in other orientations than described or illustrated herein.

**[0028]** It is to be noticed that the term "comprising", used in the claims, should not be interpreted as being restricted to the means listed thereafter; it does not exclude other elements or steps. It is thus to be interpreted as specifying the presence of the stated features, integers, steps or components as referred to, but does not preclude the presence or addition of one or more other features, integers, steps or components, or groups thereof. Thus, the scope of the expression "a device comprising means A and B" should not be limited to devices consisting only of components A and B. It means that with respect to the present invention, the only relevant components of the device are A and B.

**[0029]** Reference throughout this specification to "one embodiment" or "an embodiment" means that a particular feature, structure or characteristic described in connection with the embodiment is included in at least one embodiment of the present invention. Thus, appearances of the phrases "in one embodiment" or "in an embodiment" in various places throughout this specification are not necessarily all referring to the same embodiment, but may. Furthermore, the particular features, structures or characteristics may be combined in any suitable manner, as would be apparent to one of ordinary skill in the art from this disclosure, in one or more embodiments.

**[0030]** Similarly it should be appreciated that in the description of exemplary embodiments of the invention, various features of the invention are sometimes grouped together in a single embodiment, figure, or description thereof for the purpose of streamlining the disclosure and aiding in the understanding of one or more of the various inventive aspects. This method of disclosure, however, is not to be interpreted as reflecting an intention that the

<sup>10</sup> claimed invention requires more features than are expressly recited in each claim. Rather, as the following claims reflect, inventive aspects lie in less than all features of a single foregoing disclosed embodiment. Thus, the claims following the detailed description are hereby

<sup>15</sup> expressly incorporated into this detailed description, with each claim standing on its own as a separate embodiment of this invention.

[0031] Furthermore, while some embodiments described herein include some but not other features included in other embodiments, combinations of features of different embodiments are meant to be within the scope of the invention, and form different embodiments, as would be understood by those in the art. For example, in the following claims, any of the claimed embodiments

can be used in any combination.

**[0032]** In the description provided herein, numerous specific details are set forth. However, it is understood that embodiments of the invention may be practiced without these specific details. In other instances, well-known methods, structures and techniques have not been

shown in detail in order not to obscure an understanding of this description.

**[0033]** The present disclosure relates to integrated germanium (Ge) avalanche photodetectors in semiconductor planar technology.

[0034] In a first aspect the integrated avalanche photodetector 100, as illustrated in FIG 1, comprises a Gebody 110 adapted to conduct and optical mode. The Gebody 110 comprises a first p-doped region 120, for the absorption of an optical mode. The first p-doped region 120 extends from a first main surface 111 to a second main surface 112 of the Gebody 110. The Gebody 110 comprises a first n-doped region 130 that extends from the first main surface 111 towards the second main sur-

<sup>45</sup> face 112 of the Ge body 110. An intrinsic region 115 occupies the undoped part of the Ge body 110. A first avalanche junction is formed by the first n-doped region 130 that is located aside the p-doped region 120. The Ge body 110 comprises an incidence surface 310, suit-

<sup>50</sup> able for receiving an optical mode **300.** The incidence surface **310** is advantageously perpendicular to the first avalanche junction. The first avalanche junction is in parallel with the direction of the propagation of the optical mode as illustrated in FIG 2. The first avalanche junction

<sup>55</sup> is advantageously perpendicular to the incidence surface **310.** The Ge body **110** having a known refractive index is adapted in height and shape to conduct an optical mode along the absorption region, as known by the

skilled person. The absorption length is determined by the length of the first p-doped region **120** in the direction of the propagation of the optical mode. To maximize the absorption of light from the optical mode in the first pdoped region, it is advantageous that the absorption length is substantially equal to the length of the Ge body **110** in the direction of the propagation of the optical mode **300**, from the incidence surface **310** to the surface opposite to the incidence surface **310**. The first n-doped region **130** aside the first p-doped region, is advantageously aside the first p-doped region over the whole absorption length. The Ge body may be a GeSi compound comprising up to 10% of Si.

[0035] It has been found that a second n-doped Ge region 140 that covers the Ge body 110 and forms a second PN avalanche junction with the first p-doped region 120 at the first main surface 111 reduces the dark current of the integrated avalanche photodetector compared to the Ge avalanche photodetector according to prior art as described above. The reduction of dark current, at a given reverse bias, can be more than twice, advantageously more than four times, even more advantageously six times or more with respect to dark current in conventional prior art photodetectors such as the Ge avalanche photodetector described in the background. FIG 9 illustrates measurements of an examplary Ge photodetector according to the prior art, before (curve 1) and after reverse bias voltage stress (curves 2,3,4,5). FIG 9 demonstrates the potential reduction in dark current at different reverse bias voltages.

[0036] According to embodiments the integrated avalanche photodetector, wherein the second PN avalanche junction when in use, is reverse biased and a depletion zone is formed at the boundary of the first p-doped region 120 and the second n-doped Ge region 140. The high electric field in the depletion zone supports the avalanche multiplication as known by the skilled person. The depletion zone is spaced at least 20nm from an upper main surface 141 of the second n-doped Ge region 140. Spacing the mid-bandgap states, present at the upper main surface 141, from the depletion zone prevents the midbandgap states at the upper main surface 141 to undergo the high electric fields generated in part of the depletion zone and prevents those mid-bandgap states to contribute to the dark current increase under avalanche conditions. The high electrical field, is at least 200kV per centimetre at a reverse bias of at least -4V, to initiate and sustain avalanche multiplication when in use. The high electrical field is contained in the depletion zone and is bend away from the upper main surface 141 by the distance of the depletion zone to the upper main surface 141 caused by the spacing.

[0037] The incidence surface **310** may be perpendicular to the first avalanche junction. Allowing for evanescent coupling through the second main surface **112** to the first p-doped region **120** of the Ge body **110** and further allowing for butt-coupling through the incidence surface **310**. The upper main surface **141** may be perpendent.

dicular to the incidence surface **310**, the incidence surface **310** can then be used only in a butt-coupling configuration. In butt-coupling the optical mode can propagate through the incidence surface **310** into the Ge body

**110** in a direction parallel with the second n-doped Ge region. It should be noted that the first main surface **111** is not an incidence surface **310**.

[0038] According to embodiments, the first p-doped region 120 is advantageously not in contact with a sidewall

10 113 of the Ge body 110 perpendicular to the incidence surface 310. Thus, the electrical field in the intrinsic region is spaced from any sidewalls perpendicular to the incidence surface 310. This spacing ensures that the mid-bandgap states at those sidewalls do not contribute

<sup>15</sup> to the dark current increase under high electric fields of avalanche operation. The first p-doped region **120** is advantageously in contact with the incidence surface **310** and the with the surface of the Ge body **110** opposite to that

<sup>20</sup> [0039] According to embodiments, the first n-doped region 130 is in direct contact with the first p-doped region 120 to form a PN avalanche junction at the first avalanche junction. The PN avalanche junction further lowers the reverse bias voltage needed to create the high electrical

<sup>25</sup> field for avalanche conditions and operation.

[0040] According to embodiments, the first n-doped region 130 is spaced from the first p-doped region 120 to form a PIN avalanche junction at the first avalanche junction. The width of the intrinsic region of the PIN junction,

<sup>30</sup> caused by the spacing, is advantageously below 100nm, to allow low voltage operation. It will be readily understood that a larger width of the intrinsic region of the PIN junction is possible.

[0041] According to embodiments, the first n-doped re <sup>35</sup> gion 130 is fully extending through Ge body 110. According to embodiments the first n-doped region 130 touches the second main surface, as illustrated in FIG 2.

[0042] According to embodiments, the first n-doped region 130 is in direct contact with the sidewall 113 of the Ge body 110 perpendicular to the incidence surface 310,

as illustrated in FIG 2.

[0043] To achieve the high electrical fields required for avalanche multiplication at low reverse bias, the first p-doped region 120, the first n-doped region 130 and the

<sup>45</sup> second n-doped Ge region **140** are advantageously highly doped.

**[0044]** The intrinsic region **115** may comprise unintentionally doped Ge, lightly p-doped Ge, lightly n-doped Ge, intrinsic Ge and/or undoped Ge. Nevertheless, the doping level typically is not limiting for embodiments of the present disclosure. In some embodiments, the doping levels may be below those from the first n-doped region and the first p-doped region.

[0045] To connect the avalanche photodetector in an electrical circuit an anode electrode 160 and a cathode electrode 150 may be used. The electrical circuit may be used to reverse bias the integrated avalanche photodetector.

40

50

[0046] According to embodiments, as illustrated in FIG 3, the cathode electrode 150 is connected from the upper main surface 141. Optionally, as illustrated in FIG 4, the cathode electrode 150 may be connected through a third n-doped semiconductor region 180, which is in direct contact with the first n-doped region 130 at the second main surface 112. The anode electrode 160 may be connected to a first p-doped region 120 through a second pdoped semiconductor region 170, which is in direct contact with the first p-doped region 120 at the second main surface 112.

[0047] According to embodiments of the present disclosure, evanescent coupling of the optical mode through the second main surface 112 is possible through the second p-doped semiconductor region 170 or through the combination of the second p-doped semiconductor region 170 and the third n-doped semiconductor region 180. Evanescent coupling may be combined with buttcoupling as indicated earlier.

[0048] According to embodiments, illustrated in FIG 5, the integrated avalanche photodetector further comprises a planar integrated semiconductor waveguide 200, thereby forming an integrated waveguide avalanche photodetector. The planar integrated semiconductor waveguide 200 is configured to couple the optical mode to the Ge body 110 through the incidence surface 310. Integrated waveguide avalanche photodetectors are well known in the art, the use of Ge for absorption at the wavelengths of interest, 1300nm to 1600nm, is well known. At the frequencies of interest Si is transparent and ideal for use as waveguide, to propagate the optical mode. The Photodetector may be readily integrated in current planar semiconductor technologies. The planar integrated semiconductor waveguide 200 propagating the optical mode, is at one end configured to couple the optical mode into Ge body 110. The planar integrated semiconductor waveguide 200 is aligned with the Ge body 110, such that the direction of propagation, of the optical mode from the planar integrated semiconductor waveguide 200 into the Ge body 110, is in parallel with the first avalanche junction and that the optical mode propagates into the Ge body 110 over the absorption length. Due to the planar integration, the planar integrated semiconductor waveguide 200 has its main planar surfaces in parallel with the main surfaces 111,112 of the Ge body 110, such that the direction of propagation of the optical mode in the planar integrated semiconductor waveguide 200 and the direction of propagation of the optical mode in the Ge body 110 will be in parallel planes.

**[0049]** This coupling can for example be achieved by a butt-coupling whereby the planar integrated semiconductor waveguide **200** is terminated at the incidence surface **310** of the Ge body **110**. Alternatively evanescent coupling to the Ge body **110** can be used through the second main surface **112**, optionally combined with buttcoupling.

**[0050]** According to embodiments the integrated avalanche photodetector, wherein the second p-doped sem-

iconductor region **170**, the third n-doped semiconductor region **180** and the planar integrated semiconductor waveguide **200** are formed in a single planar semiconductor layer, as illustrated for an examplary embodiment in FIG 5.

**[0051]** The second main surface **112** of the Ge body **110** may be lower than the upper surface of the planar semiconductor layer as illustrated in FIG 3,4 and 5. The overlap of the integrated planar waveguide **200** with the

<sup>10</sup> Ge body **110** provides a first butt-coupling area, at the incidence surface **310**.

[0052] According to embodiments the integrated waveguide photodetector, may further comprise a taper 220 adapted to conduct the optical mode from the inte-

<sup>15</sup> grated semiconductor waveguide to the incidence surface **310**. The taper **220** has been found to enlarge the butt-coupling area and enhance the coupling of the optical mode into the Ge body **110**. The taper **220** can further be adapted to concentrate the optical mode in the first p<sup>20</sup> doped region **120** where the absorption of the optical

mode occurs.[0053] According to embodiments, the Ge body 110 may be epitaxial grown on a silicon (Si) layer of a SOI

substrate. The dislocations on the Si layer/Ge body interface due to the lattice mismatch can be largely alleviated by process steps as known in the art. The Si SOI has a buried oxide (BOX), the BOX is SiO2. The BOX is underneath the Si layer, and may be used as bottom cladding for the planar integrated semiconductor

waveguide 200, which may be made from the Si layer. The single planar semiconductor layer may be the Si layer of the Si SOI. The Si layer is a mono-crystalline layer. The second p-doped semiconductor region 170 may be formed in the Si layer. The third n-doped semiconductor

[0054] The Ge body 110 may comprise a dielectric 260 that covers the Ge body 110 and is advantageously SiO2, thereby leaving the mid-bandgap states at the upper main surface 141 and sidewalls 113 in contact with the

dielectric 260 intact. The dielectric 260 may be used to complete the waveguide cladding of the planar integrated

semiconductor waveguide **200** as is known in the art. The dielectric is not  $\text{GeO}_2$  as this is soluble in water it is advantageously not used. The taper **220** can for example

<sup>45</sup> be made from poly-Si on top of an etch stop layer **210**, for example a Si3N4 layer, the etch stop layer is on top of the mono-crystalline Si layer and transparent for the optical mode. SOI implementations for integrated waveguide avalanche photodetector are well known in 50 the art and will not be detailed further.

[0055] In a second aspect the present disclosure relates to the use of an avalanche photodetector according to the first aspect for detecting radiation, wherein a reverse bias is applied to the first avalanche junction and

<sup>55</sup> the second avalanche junction. The reverse bias may be applied to the n-doped regions of the junctions. The reverse bias may be applied through the second n-doped Ge region 140 optionally through the third n-doped sem-

10

iconductor region 180 or both. The reverse bias is applied to the first p-doped region 120 through the second pdoped semiconductor region 170. The anode electrode 160 and cathode electrode 150 can be used to connect to the electrical circuit that provides the reverse bias. The reverse bias maybe high enough to allow for avalanche multiplication to take place in the photodetector.

[0056] In a third aspect the present disclosure relates to a method for fabricating an integrated avalanche photodetector, the method comprising, providing an intrinsic germanium (Ge) structure that comprises: a Ge body 110 and a second Ge region that covers the Ge body 110; the Ge body 110 being adapted to conduct an optical mode; The Ge body 110 having a known refractive index is adapted in height and shape to conduct an optical mode along the absorption region, as known by the skilled person.

[0057] The method further comprises, doping the Ge structure, to form a first p-doped region 120, by implanting p-type dopants into a region extending from a first main surface 111 to a second main surface 112 of the Ge body 110. Known doping techniques may be applied to achieve a doping profile that has the main part of the ptype dopants in the Ge body and not in the second Ge region. Nevertheless, some residual doping may reside in the second Ge region.

[0058] The method further comprises, doping the Ge structure, to form a first n-doped region 130 by implanting n-type dopants into a region extending from a first main surface 111 towards a second main surface 112 of the Ge body 110. Known doping techniques may be applied to achieve a doping profile that has the main part of the n-type dopants in the Ge body and not in the second Ge region. Some residual doping may reside in the second Ge region.

[0059] The method further comprises, forming a first avalanche junction by locating the first n-doped region 130 and the first p-doped region 120 aside each other. The first p-doped region 120 and the first n-doped region 130 may be in contact to form an avalanche PN junction. Alternatively the first p-doped region 120 may be spaced from the first n-doped region 130 to form an avalanche PIN junction.

[0060] The method further comprises, providing an incidence surface 310 on the Ge body 110 suitable for optical mode incidence, perpendicular to the first avalanche iunction.

[0061] The method further comprises, doping the Ge structure, to form a second n-doped Ge region, by implanting n-type dopants into the second Ge region, the n-type dopants extending to the first main surface 111 of the Ge body 110, wherein the second n-doped Ge region covers the Ge body. Known doping techniques may be applied to achieve a doping profile that has the main part of the n-type dopants in the second Ge region and not in the Ge body 110.

[0062] It will be understood by the skilled person that doping profiles may be not abrupt and that more gradual doping transitions may exist. A certain decay in depth of the doping profile may exist in practical implementations according the embodiments of the present disclosure. FIG 6 illustrates the doping concentration of an examplary integrated avalanche photodetector according to embodiments of the present disclosure. The cross section "I" goes through the first and second n-doped region

of the Ge body 110 and shows a decay in depth towards the second main surface 112, as can be seen by the dark to light transition in FIG 6. The cross section "II" goes

through the second n-doped Ge region 140 and the first p-doped region 120. The cross section "III" goes through the second n-doped Ge region 140 and the intrinsic region 115 of the Ge body 110. FIG 7 illustrates an example

15 of applicable doping profiles, associated with the different cross sections of FIG 6, and clearly illustrates the second PN avalanche junction at cross section "II". FIG 7 further illustrates the lower doping concentration at cross section "III" with respect to cross section "I" as the depth increas-

20 es going from the first main surface 111 to the second main surface 112, due to non-abrupt doping profiles and diffusion of the dopants.

[0063] According to embodiments the method may further comprise, prior to providing the intrinsic Ge structure:

25 providing a semiconductor substrate having a buried oxide (BOX) on top; providing a semiconductor layer on top of the BOX; forming a second p-doped semiconductor region 170 in the semiconductor layer, in the location where the first p-doped region 120 will be formed; op-30 tionally forming a third n-doped semiconductor region 180 in the semiconductor layer, in the location where the first n-doped region 130 will be formed. The formation and doping of the semiconductor layer is well known in the art and will not be detailed.

35 [0064] According to embodiments, the step of providing an intrinsic germanium (Ge) structure comprises growing epitaxial Ge on part of the semiconductor layer, where the Ge structure is to be provided at the second main surface 112. Techniques for epitaxial growth of Ge

40 on semiconductor layers, for example mono-crystalline silicon, are known in the art and will not be detailed. Techniques are known in the art to minimize the impact, on dark current, of the dislocations at the semiconductor to Ge boundary cause by lattice mismatch.

45 [0065] According to embodiments, an integrated waveguide is provided in the semiconductor layer configured to couple the optical mode to the Ge body (110) formed on the semiconductor layer.

[0066] In an exemplary embodiment of the integrated 50 avalanche photodetector, provided by way of illustration in FIG 8, the Ge body has a height of 350nm measured between the first and second main surface 111,112; a width of 1000nm, measured between the two sidewalls 113; a 50nm thick second n-doped Ge region 140; a 55 500nm wide first p-doped region 120 located between the two sidewalls 113; and a 250nm wide first n-doped region 130 that extends over the full height of the Ge body **110** and is in contact with the first p-doped region

10

15

20

30

35

45

50

**120.** The configuration of FIG 8 corresponds with a photodetector having a doping distribution as illustrated in FIG 6 and FIG 7. A noticeable difference is the slanted transition at the second main surface, which is due to the formation of the Ge structure and does not affect the inventive aspect of the present disclosure.

## Claims

1. An integrated avalanche photodetector (100) comprising a Ge body (110), adapted to conduct an optical mode, the Ge body (110) comprising:

> - a first p-doped region (120), for absorption of the optical mode, extending from a first main surface (111) to a second main surface (112) of the Ge body (110), and;

- a first n-doped region (130) aside the first pdoped region (120), and extending from the first main surface (111) towards the second main surface (112) of the Ge body (110), forming a first avalanche junction with the first p-doped region (120);

- an intrinsic region (115) that occupies the un- <sup>25</sup> doped part of the Ge body (110);

- an incidence surface (310) suitable for receiving the optical mode perpendicular to the first avalanche junction;

**characterized in that** a second n-doped Ge region (140) covers the Ge body (110) and forms a second PN avalanche junction with the first p-doped region (120) at the first main surface (111).

- 2. The avalanche photodetector according to claim 1, wherein a depletion zone of the second PN avalanche junction, when in use, is spaced at least 20nm from an upper main surface (141) of the second ndoped Ge region (140).

- The avalanche photo detector according to any of the preceding claims, wherein the second n-doped Ge region (140) has the upper main surface (141) perpendicular to the incidence surface (310).

- 4. The avalanche photo detector according to any of the preceding claims, wherein;

- the second n-doped Ge region (140) is connected to a cathode electrode (150) from the upper main surface (141) of the second n-doped Ge region (140), and ;

- the first p-doped region (120) is connected to an anode electrode (160) through a second pdoped semiconductor region (170), which is in direct contact with the first p-doped region (120) at the second main surface (112).

- The avalanche photodetector according to any of the preceding claims, wherein the first p-doped region (120) is not in contact with a sidewall (113) of the Ge body (110) perpendicular to the incidence surface (310).

- The avalanche photodetector according to any of the preceding claims, wherein the first n-doped region (130) is in direct contact with the first p-doped region (120) and the first avalanche junction is a PN avalanche junction.

- 7. The avalanche photodetector according to claims 1-5 wherein the first n-doped region (130) is spaced from the first p-doped region (120) and the first avalanche junction is a PIN avalanche junction.

- **8.** The avalanche photo detector according to any of the preceding claims, wherein;

- the first n-doped region (130) is fully extending through Ge body (110) and is connected to the cathode electrode (150) through a third n-doped semiconductor region (180), which is in direct contact with the first n-doped region (130) at the second main surface (112), and ;

- the first p-doped region (120) is connected to the anode electrode (160) through the second p-doped semiconductor region (170), which is in direct contact with the first p-doped region (120) at the second main surface (112).

- 9. The avalanche photodetector according to any of the preceding claims, further comprises a planar integrated semiconductor waveguide (200) configured to couple the optical mode to the Ge body (110) through the incidence surface (310), thereby forming an integrated waveguide avalanche photodetector.

- 40 10. The avalanche photodetector according to claim 9, further comprising a taper (220) adapted to conduct the optical mode from the integrated semiconductor waveguide to the incidence surface (310).

- The avalanche photo detector according to claim 9-10, wherein the second p-doped semiconductor region (170), the third n-doped semiconductor region (180) and the integrated semiconductor waveguide are formed in a single planar semiconductor layer.

- **12.** The avalanche photo detector according to claim 11, wherein the planar semiconductor layer is silicon and the Ge body (110) is covered with silicon oxide (260).

- <sup>55</sup> **13.** The use of the avalanche photodetector according to claims 1-12, wherein a reverse bias is applied to the first avalanche junction and the second avalanche junction.

**14.** A method for fabricating an integrated avalanche photo detector, the method comprising:

- providing a Ge body (110) of intrinsic germanium adapted to conduct an optical mode;

- doping a region, extending from a first main surface (111) to a second main surface (112) of the Ge body (110), with a p-type dopant to obtain a first p-doped region (120);

doping a region, extending from the first main <sup>10</sup> surface (111) towards the second main surface (112) of the Ge body (110), with a n-type dopant to obtain a first n-doped region (130);

- forming a first avalanche junction with the first n-doped region (130) located aside the first p- <sup>15</sup> doped region (120);

- providing an incidence surface (310) on the Ge body (110) suitable for optical mode incidence, perpendicular to the first avalanche junction;

- providing a second n-doped Ge region (140) <sup>20</sup> that covers the Ge body (110) to form a second PN avalanche junction with the first p-doped region (120) at the first main surface (111).

**15.** The method according to claim 14, wherein providing <sup>25</sup> the Ge body (110) comprises:

- providing a semiconductor layer;

- forming a second p-doped semiconductor region (170) in the semiconductor layer, in the location where the first p-doped region (120) will be formed;

- optionally forming a third n-doped semiconductor region (180) in the semiconductor layer, in the location where the first n-doped region (130) <sup>35</sup> will be formed;

- after doping the semiconductor layer, providing the Ge body (110) on top of and in contact with the semiconductor layer at the second main surface (112).

45

40

50

55

FIG.2

FIG.4

FIG.5

Doping distribution

FIG.7

FIG.9

# EP 3 038 167 A1

## **EUROPEAN SEARCH REPORT**

Application Number EP 15 15 2513

|    |                                | DOCUMENTS CONSID                                                                                                                                                    | ]                                                                                                    |                                                                                                                                                                                                            |                                                    |  |

|----|--------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|--|

|    | Category                       | Citation of document with in of relevant passa                                                                                                                      | ndication, where appropriate,<br>ages                                                                | Relevant<br>to claim                                                                                                                                                                                       | CLASSIFICATION OF THE<br>APPLICATION (IPC)         |  |

| 10 | A                              | US 7 397 101 B1 (MA<br>ET AL) 8 July 2008<br>* pages 7a, 8a *                                                                                                       | SINI GIANLORENZO [US]<br>(2008-07-08)                                                                | 1-15                                                                                                                                                                                                       | INV.<br>H01L31/107<br>H01L31/18                    |  |

| 15 | A                              | VU V A ET AL: "PIN<br>Photodetector Fabri<br>Manufacturability",<br>IEEE TRANSACTIONS O<br>MANUFACTURING, IEEE<br>PISCATAWAY, NJ, US,                               | cation Issues and<br>N SEMICONDUCTOR<br>SERVICE CENTER,                                              | 1-15                                                                                                                                                                                                       |                                                    |  |

| 20 |                                |                                                                                                                                                                     | ugust 2010 (2010-08-01)                                                                              |                                                                                                                                                                                                            |                                                    |  |

| 25 | A                              | EP 2 736 084 A1 (IM<br>28 May 2014 (2014-0<br>* the whole documen                                                                                                   | 5-28)                                                                                                | 1-15                                                                                                                                                                                                       |                                                    |  |

| 30 |                                |                                                                                                                                                                     |                                                                                                      |                                                                                                                                                                                                            | TECHNICAL FIELDS<br>SEARCHED (IPC)<br>H01L<br>G02B |  |

| 35 |                                |                                                                                                                                                                     |                                                                                                      |                                                                                                                                                                                                            |                                                    |  |

| 40 |                                |                                                                                                                                                                     |                                                                                                      |                                                                                                                                                                                                            |                                                    |  |

| 45 |                                |                                                                                                                                                                     |                                                                                                      |                                                                                                                                                                                                            |                                                    |  |

| 1  | L                              | The present search report has be<br>Place of search                                                                                                                 | Deen drawn up for all claims                                                                         |                                                                                                                                                                                                            | Examiner                                           |  |

| 50 | 401)                           | Berlin                                                                                                                                                              | 10 July 2015                                                                                         | Le                                                                                                                                                                                                         | Meur, M                                            |  |

|    | X:par<br>X:par<br>Y:par<br>doc | ATEGORY OF CITED DOCUMENTS<br>ticularly relevant if taken alone<br>ticularly relevant if combined with anoth<br>ument of the same category<br>nnological background | E : earlier patent doo<br>after the filing dat<br>ner D : document cited ir<br>L : document cited fo | T : theory or principle underlying the inventio<br>E : earlier patent document, but published or<br>after the filing date<br>D : document cited in the application<br>L : document cited for other reasons |                                                    |  |

| 55 | O : nor                        |                                                                                                                                                                     |                                                                                                      | & : member of the same patent family, corresponding<br>document                                                                                                                                            |                                                    |  |

## EP 3 038 167 A1

## ANNEX TO THE EUROPEAN SEARCH REPORT ON EUROPEAN PATENT APPLICATION NO.

EP 15 15 2513

5

This annex lists the patent family members relating to the patent documents cited in the above-mentioned European search report. The members are as contained in the European Patent Office EDP file on The European Patent Office is in no way liable for these particulars which are merely given for the purpose of information.

10-07-2015

| 10    | Patent document<br>cited in search report |    | Publication<br>date | Patent family<br>member(s)                           | Publication<br>date                    |

|-------|-------------------------------------------|----|---------------------|------------------------------------------------------|----------------------------------------|

|       | US 7397101                                | B1 | 08-07-2008          | NONE                                                 |                                        |

| 15    | EP 2736084                                | A1 | 28-05-2014          | EP 2736084 A1<br>JP 2014107562 A<br>US 2014138787 A1 | 28-05-2014<br>09-06-2014<br>22-05-2014 |

| 20    |                                           |    |                     |                                                      |                                        |

| 25    |                                           |    |                     |                                                      |                                        |

| 30    |                                           |    |                     |                                                      |                                        |

| 35    |                                           |    |                     |                                                      |                                        |

| 10    |                                           |    |                     |                                                      |                                        |

| 5     |                                           |    |                     |                                                      |                                        |

| 60    |                                           |    |                     |                                                      |                                        |

| 55 55 | or more details about this annea          |    |                     |                                                      |                                        |

## **REFERENCES CITED IN THE DESCRIPTION**

This list of references cited by the applicant is for the reader's convenience only. It does not form part of the European patent document. Even though great care has been taken in compiling the references, errors or omissions cannot be excluded and the EPO disclaims all liability in this regard.

### Non-patent literature cited in the description

• Silicon Optical Interconnect Device Technologies for 40Gb/s and beyond. *IEEE journal of selected topics in quantum electronics*, March 2013, vol. 19 (2 [0005]